| 번호 | 청구항 |

|---|---|

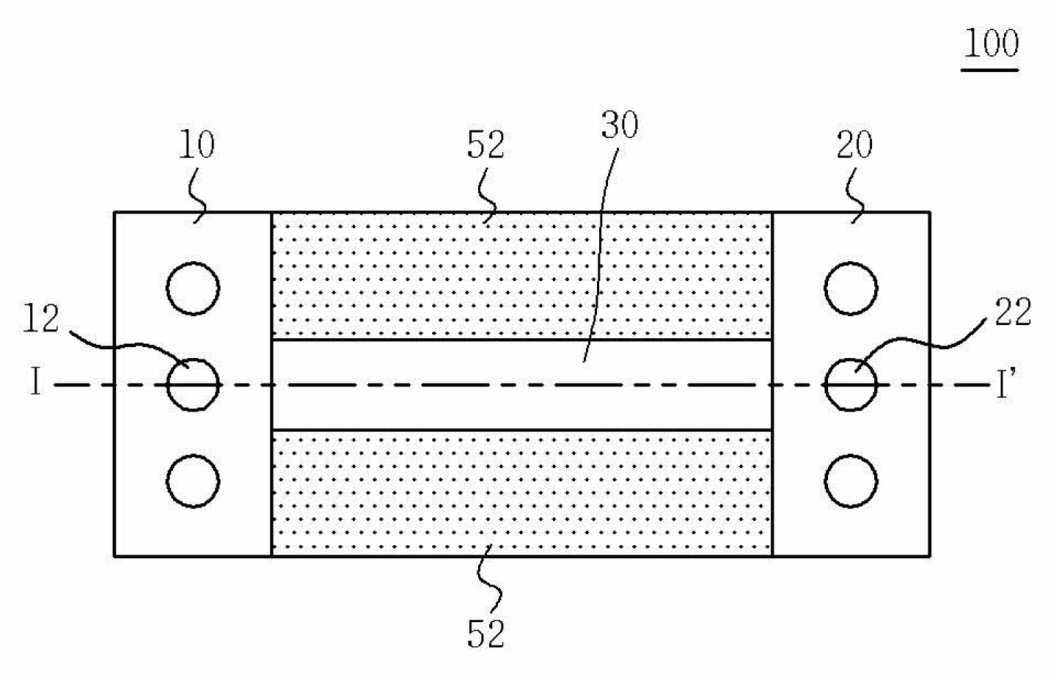

| 1 | 제1 및 제2 전극을 상호 연결하는 게이트 메탈;상기 게이트 메탈의 하부에 형성되는 제1 산화물층; 및상기 게이트 메탈의 하단과 상기 제1 산화물층의 상단 사이에 형성되는 게이트 산화물층;상기 게이트 메탈의 하부 및 상기 제1 산화물층의 양측에 형성되는 반도체층;을 포함하는 반도체 장치의 이-퓨즈. |

| 2 | 제 1 항에 있어서,상기 제1 산화물층은 상기 게이트 메탈의 중앙에 대응하는 하부에 형성되는 반도체 장치의 이-퓨즈. |

| 3 | 삭제 |

| 4 | 제 1 항에 있어서,상기 게이트 메탈의 상부에 형성되는 실리콘 질화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |

| 5 | 제 4 항에 있어서,상기 실리콘 질화물층, 상기 반도체층 및 상기 제1 산화물층의 상부에 형성되는 제2 산화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |

| 6 | 제 1 항에 있어서,상기 게이트 산화물층은, 상기 게이트 메탈의 하부에 형성되고 상기 게이트 메탈의 하부에 대응하는 상기 제1 산화물층의 상단에 접하는 반도체 장치의 이-퓨즈. |

| 7 | 제 1 항에 있어서,상기 제1 및 제2 전극과 상기 게이트 메탈의 상부에 형성되는 실리콘 질화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |

| 8 | 제 7 항에 있어서,상기 실리콘 질화물층 및 상기 제1 산화물층의 상부에 형성되는 제2 산화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |

| 9 | 제 1 항에 있어서,상기 게이트 메탈은, NMOS 또는 PMOS에 사용되는 엔-타입 또는 피-타입의 메탈로 형성되는 반도체 장치의 이-퓨즈. |

| 10 | 제1 전극에서 연장되는 제1 게이트 메탈;제2 전극에서 상기 제1 게이트 메탈과 접촉되도록 연장되는 제2 게이트 메탈;상기 제1 및 제2 게이트 메탈의 하부에 형성되는 제1 산화물층; 및상기 제1 및 제2 게이트 메탈의 하단과 상기 제1 산화물층의 상단 사이에 형성되는 게이트 산화물층;상기 제1 및 제2 게이트 메탈의 하부 및 상기 제1 산화물층의 양측에 형성되는 반도체층;을 포함하는 반도체 장치의 이-퓨즈. |

| 11 | 삭제 |

| 12 | 제 10 항에 있어서,상기 제1 및 제2 게이트 메탈은 서로 다른 메탈로 형성되는 반도체 장치의 이-퓨즈. |

| 13 | 제 12 항에 있어서,상기 제1 게이트 메탈은 NMOS에 사용되는 엔-타입의 메탈로 형성되고, 상기 제2 게이트 메탈은 PMOS에 사용되는 피-타입의 메탈로 형성되는 반도체 장치의 이-퓨즈. |

| 14 | 제 10 항에 있어서,상기 게이트 산화물층은, 상기 제1 및 제2 게이트 메탈의 하부에 형성되고 상기 제1 및 제2 게이트 메탈의 하부에 대응하는 상기 제1 산화물층의 상단에 접하는 반도체 장치의 이-퓨즈. |

| 15 | 제 10 항에 있어서,상기 게이트 메탈의 상부에 형성되는 실리콘 질화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |

| 16 | 제 15 항에 있어서,상기 실리콘 질화물층, 및 상기 제1 산화물층의 상부에 형성되는 제2 산화물층;을 더 포함하는 반도체 장치의 이-퓨즈. |