| 번호 | 청구항 |

|---|---|

| 1 | 메모리 장치에 있어서,복수의 워드 라인들을 제어하고, 활성화 값에 적용되는 가중치 값에 따라 제1 턴-온 전압을 인가하는 워드 라인을 선택하도록 구성되는 워드 라인 디코더;상기 복수의 워드 라인들 중 제1 워드 라인과 및 제2 워드 라인을 포함하는 워드 라인들과 각각 연결되는 메모리 셀들을 포함하는 제1 메모리 셀 어레이; 및상기 제1 메모리 셀 어레이와 제1 비트 라인 및 제1 반전 비트 라인을 통해 연결되고, 상기 제1 비트 라인을 통해 수신하는 제1 입력과 상기 제1 반전 비트 라인을 통해 수신하는 제2 입력을 더하여 제1 최초 연산 결과를 생성하도록 구성되는 시프트 덧셈기를 포함하고,상기 제1 메모리 셀 어레이는 제1 비트 및 제2 비트를 포함하는 제1 활성화 값을 저장하고,상기 제1 비트는 상기 제1 워드 라인과 연결되는 제1 메모리 셀에 저장되고,상기 제2 비트는 상기 제2 워드 라인과 연결되는 제2 메모리 셀에 저장되는 메모리 장치. |

| 2 | 제 1 항에 있어서,상기 워드 라인 디코더는 복수의 반전 워드 라인들을 제어하고, 가중치 값에 따라, 제2 턴-온 전압을 인가하는 반전 워드 라인을 선택하도록 더 구성되고,상기 복수의 반전 워드 라인들은 상기 제1 메모리 셀 어레이에 포함되는 상기 복수의 메모리 셀들과 각각 연결되는 반전 워드 라인들을 포함하는 메모리 장치. |

| 3 | 제 2 항에 있어서,상기 시프트 덧셈기에 상기 제1 입력의 부호 정보, 및 상기 제2 입력의 부호 정보를 제공하도록 구성되는 시프트 덧셈기 컨트롤러를 더 포함하는 메모리 장치. |

| 4 | 제 3 항에 있어서,상기 시프트 덧셈기는:상기 제1 비트 라인과 제1 입력단이 연결되고, 제2 입력단으로 논리 0을 수신하고, 상기 제1 입력의 부호 정보에 응답하여 제1 출력 값을 선택하도록 구성되는 제1 다중화기;상기 제1 반전 비트 라인을 입력으로 갖는 NOT 게이트; 및상기 NOT 게이트의 출력단을 제1 입력단으로 갖고, 논리 0을 제2 입력단으로 수신하고, 상기 제2 입력의 부호 정보에 응답하여, 제2 출력 값을 선택하도록 구성되는 제2 다중화기;상기 제1 비트 라인과 제1 입력단이 연결되고, 제2 입력단으로 논리 0을 수신하고, 상기 부호 정보의 반전 신호에 응답하여 제3 출력 값을 선택하도록 구성되는 제3 다중화기; 및상기 제1 비트 라인과 제1 입력단이 연결되고, 제2 입력단으로 상기 제1 다중화기의 제1 출력 값을 수신하고, 상기 부호 정보에 응답하여 제4 출력 값을 선택하도록 구성되는 제4 다중화기를 포함하고,제1 출력 값, 제2 출력 값, 제3 출력 값, 및 제4 출력 값을 기반으로, 상기 제1 최초 연산 결과를 생성하는 메모리 장치. |

| 5 | 제 4 항에 있어서,상기 연산 결과는 최상위 비트, 중간 비트, 및 최하위 비트를 포함하는 3비트로 구성되고,상기 시프트 덧셈기는:상기 NOT 게이트의 출력 값 및 상기 제3 출력 값을 더하고, 제1 캐리 및 상기 연산 결과의 상기 최하위 비트를 출력하도록 구성되는 반 덧셈기;상기 제1 캐리, 상기 제2 출력 값, 및 상기 제4 출력 값을 더하고, 제2 캐리 및 상기 연산 결과의 상기 중간 비트를 출력하도록 구성되는 제1 전 덧셈기; 및상기 제2 캐리, 상기 제1 출력 값, 및 상기 제2 출력 값을 더하고, 상기 연산 결과의 상기 최상위 비트를 출력하도록 구성되는 제2 전 덧셈기를 포함하는 메모리 장치. |

| 6 | 제 3 항에 있어서,상기 시프트 덧셈기는 제1 시프트 덧셈기이고,상기 복수의 워드 라인들 중 제5 워드 라인 및 제6 워드 라인과 각각 연결되는 메모리 셀들을 포함하는 제2 메모리 셀 어레이;상기 제2 메모리 셀 어레이와 상기 제1 비트 라인 및 상기 제1 반전 비트 라인을 통해 연결되고, 상기 제1 비트 라인을 통해 수신하는 제3 입력, 및 상기 제1 반전 비트 라인을 통해 수신하는 제4 입력을 더하여 제2 최초 연산 결과를 생성하도록 구성되는 제2 시프트 덧셈기; 및상기 제1 시프트 덧셈기 및 상기 제2 시프트 덧셈기와 연결되고, 상기 제1 최초 연산 결과 및 상기 제2 최초 연산 결과를 더하도록 구성되는 덧셈 트리를 더 포함하는 메모리 장치. |

| 7 | 제 6 항에 있어서,상기 제2 메모리 셀 어레이는 제5 비트 및 제6 비트를 포함하는 제3 활성화 값을 저장하고,상기 제5 비트는 상기 제5 워드 라인과 연결되는 제5 메모리 셀에 저장되고,상기 제6 비트는 상기 제6 워드 라인과 연결되는 제6 메모리 셀에 저장되는 메모리 장치. |

| 8 | 제 7 항에 있어서,상기 제1 메모리 셀은:상기 제1 비트 라인 및 제1 노드 사이에 연결되고, 게이트 노드가 상기 제1 워드 라인과 연결되는 NMOS 트랜스터(n-type metal-oxide-semiconductor transistor);상기 제1 반전 비트 라인 및 제2 노드와 연결되고, 게이트 노드가 제1 반전 워드 라인과 연결되는 PMOS 트랜지스터(p-type metal-oxide-semiconductor transistor);상기 제1 노드를 입력단으로 갖고, 상기 제2 노드를 출력단으로 갖는 제1 인버터(inverter); 및상기 제2 노드를 입력단으로 갖고, 상기 제1 노드를 출력단으로 갖는 제2 인버터를 포함하는 메모리 장치. |

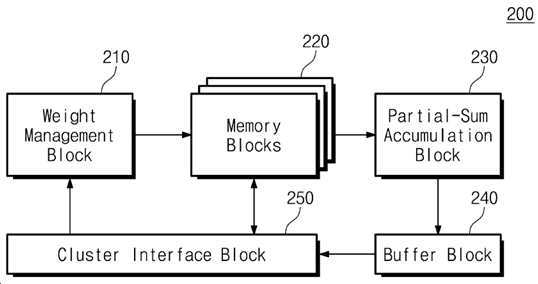

| 9 | 메모리 내 연산 제공 메모리 장치의 동작 방법에 있어서,복수의 워드 라인들과 연결되는 복수의 메모리 셀들을 포함하는 메모리 셀 어레이에 저장되는 제1 활성화 값, 및 제2 활성화 값의 부호를 결정하는 단계;상기 제1 활성화 값에 적용될 제1 가중치의 부호 및 상기 제2 활성화 값에 적용될 제2 가중치의 부호를 결정하는 단계; 및상기 제1 활성화 값에 상기 제1 가중치를 적용한 제1 연산 결과 및 상기 제2 활성화 값에 상기 제2 가중치를 적용한 제2 연산 결과를 자릿수들 별로 더하는 단계를 포함하고,상기 제1 활성화 값은 상기 복수의 워드 라인들 중 제1 워드 라인 및 제2 워드 라인을 포함하는 워드 라인들과 각각 연결되는 제1 메모리 셀들에 저장되고,상기 제1 가중치는 상기 복수의 워드 라인들 중 제1 턴-온 전압이 인가되는 워드 라인을 선택하는 것을 기반으로, 상기 제1 활성화 값에 적용되는 동작 방법. |

| 10 | 가속기에 있어서,상기 가속기를 제어하고, 상기 가속기의 동작을 수행하도록 구성되는 프로세싱 부; 및상기 가속기의 데이터를 저장하고, 메모리 내 연산을 제공하도록 구성되는 메모리 클러스터 모듈을 포함하고,상기 메모리 클러스터 모듈은:활성화 값들을 포함하는 상기 데이터를 저장하고 상기 활성화 값들 간의 가중치 연산을 수행하도록 구성되는 메모리 블록;가중치들을 상기 활성화 값들에 적용하도록 상기 메모리 블록을 제어하도록 구성되는 가중치 관리 블록; 및상기 메모리 블록이 생성한 최초 연산 결과를 합하여, 최종 연산 결과를 생성하도록 구성되는 부분 합 누적 블록을 포함하고,상기 메모리 블록은:제1 워드 라인 및 제2 워드 라인을 포함하는 복수의 워드 라인들을 제어하고, 제1 턴-온 전압을 인가하는 워드 라인을 선택하는 것을 기반으로, 상기 가중치들을 상기 활성화 값들에 적용하도록 구성되는 워드 라인 디코더; 및상기 복수의 워드 라인들과 연결되고, 제1 비트 및 제2 비트를 포함하는 제1 활성화 값을 저장하도록 구성되는 메모리 셀 어레이를 포함하고,상기 제1 비트는 제1 워드 라인과 연결되는 제1 메모리 셀에 저장되고, 상기 제2 비트는 상기 제2 워드 라인과 연결되는 제2 메모리 셀에 저장되는 가속기. |