| 번호 | 청구항 |

|---|---|

| 1 | 임피던스 캘리브레이션 커맨드를 수신하고, 상기 임피던스 캘리브레이션 커맨드에 기초하여 캘리브레이션 인에이블 신호를 생성하는 캘리브레이션 컨트롤러; 및기판에 형성되는 외부 저항에 임피던스 패드를 통하여 연결되고, 상기 캘리브레이션 인에이블 신호에 응답하여 초기 풀업 제어 코드에 기초한, 상기 임피던스 패드에 연결되는 제1 노드의 제1 전압과 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제1 전압과 동일할 때의 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 제1 노드를 구동하는 풀업 제어 코드를 생성하고, 상기 풀업 제어 코드에 기초한, 제2 노드의 제2 전압과 상기 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제2 전압과 동일할 때의 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 제2 노드를 구동하는 풀다운 제어 코드를 생성하는 캘리브레이션 회로를 포함하는 임피던스 캘리브레이션 회로. |

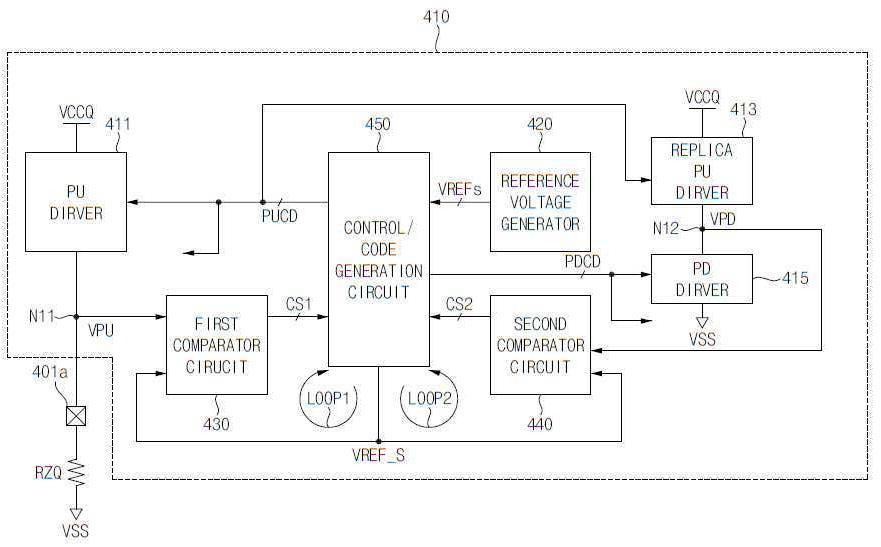

| 2 | 제1항에 있어서, 상기 캘리브레이션 회로는전원 전압과 상기 제1 노드 사이에 연결되고, 상기 초기 풀업 제어 코드에 기초하여 상기 제1 노드를 상기 제1 전압으로 구동하는 풀업 드라이버;상기 제1 전압과 상기 선택된 기준 전압을 비교하여 제1 비교 신호를 생성하는 제1 비교기 회로;복수의 기준 전압들을 생성하는 기준 전압 생성기; 상기 전원 전압과 상기 제2 노드 사이에 연결되고, 상기 풀업 제어 코드에 기초하여 상기 제2 노드를 상기 제2 전압으로 구동하는 레플리카 풀업 드라이버;상기 제2 노드와 접지 전압 사이에 연결되는 풀다운 드라이버; 상기 제2 전압과 상기 선택된 기준 전압을 비교하여 제2 비교 신호를 생성하는 제2 비교기 회로;상기 복수의 기준 전압들에서 상기 선택된 기준 전압을 선택하고, 상기 제1 비교 신호에 기초하여 상기 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 풀업 제어 코드를 생성하고, 상기 제2 비교 신호에 기초하여 상기 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 풀다운 제어 코드를 생성하고, 상기 풀다운 제어 코드를 상기 풀다운 드라이버에 제공하는 제어/코드 생성 회로를 포함하는 것을 특징으로 하는 임피던스 캘리브레이션 회로. |

| 3 | 제2항에 있어서, 상기 제어/코드 생성 회로와 상기 제1 비교기 회로는 제1 루프를 구성하여 상기 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 풀업 제어 코드를 생성하고,상기 제어/코드 생성 회로와 상기 제2 비교기 회로는 제2 루프를 구성하여 상기 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 풀다운 제어 코드를 생성하고,상기 캘리브레이션 인에이블 신호에 응답하여 클럭 신호를 생성하는 발진기를 더 포함하고,상기 제어/코드 생성 회로는상기 클럭 신호에 기초하여 선택 신호들과 반전 선택 신호들을 생성하는 선택 신호 생성기;상기 선택 신호들과 상기 반전 선택 신호들에 기초하여 복수의 사이클들 각각 동안에 상기 복수의 기준 전압들 중 적어도 일부를 선택하여 상기 선택된 기준 전압을 출력하는 기준 전압 선택기;상기 제1 비교 신호에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제1 전압과 동일할 때의 상기 제1 기준 전압 코드를 산출하는 제1 기준 전압 코드 생성기; 상기 클럭 신호와 상기 제1 기준 전압 코드에 기초하여 상기 풀업 제어 코드를 생성하는 풀업 코드 생성기;상기 제2 비교 신호에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제2 전압과 동일할 때의 상기 제2 기준 전압 코드를 산출하는 제2 기준 전압 코드 생성기; 및상기 클럭 신호와 상기 제2 기준 전압 코드에 기초하여 상기 풀다운 제어 코드를 생성하는 풀다운 코드 생성기를 포함하는 것을 특징으로 하는 임피던스 캘리브레이션 회로. |

| 4 | 제3항에 있어서, 상기 선택 신호 생성기는상기 클럭 신호에 기초하여 순차적으로 활성화되는 복수의 시퀀스 신호들을 생생하는 시퀀스 생성기;상기 복수의 시퀀스 신호들에 기초하여 상기 복수의 사이클들과 관련되는 복수의 사이클 신호들을 생성하는 사이클 정보 생성기; 상기 복수의 사이클 신호들에 기초하여 상기 선택 신호들를 생성하는 신호 생성기; 및상기 선택 신호들을 반전시켜 상기 반전 선택 신호들을 출력하는 인버터를 포함하고,상기 기준 전압 생성기는 상기 전원 전압과 상기 접지 전압 사이에 연결되는 복수의 저항들을 포함하는 저항-래더(resistor-ladder) 타입이고, 상기 제1 비교기 회로는 복수의 비교기들을 포함하고, 상기 복수의 비교기들은 상기 제1 전압과 상기 복수의 기준 전압들 중 일부를 비교하여 복수의 비교 신호들을 상기 제1 비교 신호로서 출력하고, 상기 제1 기준 전압 코드 생성기는 상기 복수의 비교 신호들을 인코딩하여 상기 제1 기준 전압 코드를 생성하는 것을 특징으로 하는 임피던스 캘리브레이션 회로. |

| 5 | 제3항에 있어서, 상기 풀업 코드 생성기는상기 클럭 신호와 제1 기준 전압 코드에 기초하여 복수의 합산 신호들을 생성하는 이진 분주 회로; 및상기 합산 신호들 중 최상위 합산 신호와 상기 클럭 신호에 기초하여 상기 풀업 제어 코드의 비트들을 순차적으로 생성하는 쉬프트 레지스터를 포함하고,상기 이진 분주 회로는상기 초기 풀업 제어 코드와 동일한 제1 초기 설정값과 상기 클럭 신호를 이용하는 제1 그룹의 디-플립플롭들; 및상기 제1 기준 전압 코드의 비트들과 상기 제1 그룹의 디-플립플롭들의 출력들에 기초하여 상기 복수의 합산 신호들을 생성하는 복수의 전가산기들을 포함하고,상기 쉬프트 레지스터는 제2 그룹의 직렬 연결된 디-플립플롭들을 포함하고, 상기 제2 그룹의 디-플립플롭들 중 제1 디-플립플롭은 상기 최상위 합산 신호와 상기 클럭 신호에 기초하여 출력 단자에서 상기 풀업 제어 코드의 비트들 중 제1 비트를 출력하고,상기 제2 그룹의 디-플립플롭들 중 상기 제1 디-플립플롭을 제외한 나머지 디-플립플롭들 각각은 상기 클럭 신호를 수신하는 클럭 단자, 상기 이전 디-플립플롭의 출력 단자에 연결되는 데이터 단자 및 출력 단자를 포함하고, 상기 출력 단자에서 단자에서 상기 풀업 제어 코드의 비트들 중 상응하는 비트를 출력하는 것을 특징으로 하는 임피던스 캘리브레인션 회로. |

| 6 | 제3항에 있어서, 상기 풀업 코드 생성기는상기 제1 기준 전압 코드에 기초하여 감산기 코드를 생성하는 감산기;상기 클럭 신호 및 상기 감산기 코드에 기초하여 복수의 합산 신호들을 생성하는 이진 분주 회로; 및상기 합산 신호들 중 최상위 합산 신호와 상기 클럭 신호에 기초하여 상기 풀업 제어 코드의 비트들을 순차적으로 생성하는 쉬프트 레지스터를 포함하는 것을 특징으로 하는 임피던스 캘리브레이션 회로. |

| 7 | 제6항에 있어서, 상기 감산기는상기 제1 기준 전압 코드와 상기 제1 기준 전압 코드의 2의 보수에 기초하여 상기 감산기 코드를 생성하고,상기 이진 분주 회로는상기 초기 풀업 제어 코드와 동일한 제1 설정값과 상기 클럭 신호를 이용하는 제1 그룹의 디-플립플롭들; 및상기 감산기 코드의 비트들과 상기 제1 그룹의 디-플립플롭들의 출력들에 기초하여 상기 복수의 합산 신호들을 생성하는 복수의 전가산기들을 포함하고,상기 쉬프트 레지스터는 직렬 연결된 제2 그룹의 디-플립플롭들을 포함하고, 상기 제2 그룹의 디-플립플롭들 중 제1 디-플립플롭은 상기 최상위 합산 신호와 상기 클럭 신호에 기초하여 출력 단자에서 상기 풀업 제어 코드의 비트들 중 제1 비트를 출력하고,상기 제2 그룹의 디-플립플롭들 중 상기 제1 디-플립플롭을 제외한 나머지 디-플립플롭들 각각은 상기 클럭 신호를 수신하는 클럭 단자, 상기 이전 디-플립플롭의 출력 단자에 연결되는 데이터 단자 및 출력 단자를 포함하고, 상기 출력 단자에서 단자에서 상기 풀업 제어 코드의 비트들 중 상응하는 비트를 출력하는 것을 특징으로 하는 임피던스 캘리브레이션 회로. |

| 8 | 기판에 형성되는 외부 저항; 및상기 외부 저항에 공통으로 연결되며 상기 기판에 실장되는 복수의 메모리 다이들을 포함하고,상기 복수의 메모리 다이들 각각은상기 외부 저항에 임피던스 패드를 통하여 연결되고, 임피던스 캘리브레이션 커맨드에 응답하여 초기 풀업 제어 코드에 기초한, 상기 임피던스 패드에 연결되는 제1 노드의 제1 전압과 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제1 전압과 동일할 때의 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 제1 노드를 구동하는 풀업 제어 코드를 생성하고, 상기 풀업 제어 코드에 기초한, 제2 노드의 제2 전압과 상기 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제2 전압과 동일할 때의 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 제2 노드를 구동하는 풀다운 제어 코드를 생성하는 임피던스 캘리브레이션 동작을 수행하는 임피던스 캘리브레이션 회로를 포함하는 반도체 메모리 장치. |

| 9 | 제8항에 있어서, 상기 임피던스 캘리브레이션 회로는상기 임피던스 캘리브레이션 커맨드를 수신하고, 상기 임피던스 캘리브레이션 커맨드에 기초하여 캘리브레이션 인에이블 신호를 생성하는 캘리브레이션 컨트롤러; 및상기 외부 저항에 상기 임피던스 패드를 통하여 연결되고, 상기 캘리브레이션 인에이블 신호에 응답하여 상기 임피던스 캘리브레이션 동작을 수행하는 캘리브레이션 회로를 포함하고,상기 캘리브레이션 회로는전원 전압과 상기 제1 노드 사이에 연결되고, 상기 초기 풀업 제어 코드에 기초하여 상기 제1 노드를 상기 제1 전압으로 구동하는 풀업 드라이버;상기 제1 전압과 상기 선택된 기준 전압을 비교하여 제1 비교 신호를 생성하는 제1 비교기 회로;복수의 기준 전압들을 생성하는 기준 전압 생성기; 상기 전원 전압과 상기 제2 노드 사이에 연결되고, 상기 풀업 제어 코드에 기초하여 상기 제2 노드를 상기 제2 전압으로 구동하는 레플리카 풀업 드라이버;상기 제2 노드와 접지 전압 사이에 연결되는 풀다운 드라이버; 상기 제2 전압과 상기 선택된 기준 전압을 비교하여 제2 비교 신호를 생성하는 제2 비교기 회로;상기 복수의 기준 전압들에서 상기 선택된 기준 전압을 선택하고, 상기 제1 비교 신호에 기초하여 상기 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 풀업 제어 코드를 생성하고, 상기 제2 비교 신호에 기초하여 상기 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 풀다운 제어 코드를 생성하고, 상기 풀다운 제어 코드를 상기 풀다운 드라이버에 제공하는 제어/코드 생성 회로를 포함하는 것을 특징으로 하는 반도체 메모리 장치. |

| 10 | 임피던스 캘리브레이션 커맨드를 수신하고, 상기 임피던스 캘리브레이션 커맨드에 기초하여 캘리브레이션 인에이블 신호를 생성하는 캘리브레이션 컨트롤러; 및기판에 형성되는 외부 저항에 임피던스 패드를 통하여 연결되고, 상기 캘리브레이션 인에이블 신호에 응답하여 초기 다운 제어 코드에 기초한, 상기 임피던스 패드에 연결되는 제1 노드의 제1 전압과 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제1 전압과 동일할 때의 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 제1 노드를 구동하는 풀다운 제어 코드를 생성하고, 상기 풀다운 제어 코드에 기초한, 제2 노드의 제2 전압과 상기 선택된 기준 전압의 비교에 기초하여 상기 선택된 기준 전압의 레벨이 상기 제2 전압과 동일할 때의 제2 기준 전압 코드를 산출하고, 상기 제2 기준 전압 코드에 기초하여 상기 제2 노드를 구동하는 풀업 제어 코드를 생성하는 캘리브레이션 회로를 포함하고,상기 캘리브레이션 회로는상기 제1 노드와 전원 전압 사이에 연결되고, 상기 초기 풀다운 제어 코드에 기초하여 상기 제1 노드를 상기 제1 전압으로 구동하는 풀다운 드라이버;상기 제1 전압과 상기 선택된 기준 전압을 비교하여 비교 신호를 생성하는 비교기 회로;복수의 기준 전압들을 생성하는 기준 전압 생성기; 및상기 복수의 기준 전압들 중 적어도 일부를 선택하여 상기 선택된 기준 전압을 제공하고, 상기 비교 신호에 기초하여 상기 제1 기준 전압 코드를 산출하고, 상기 제1 기준 전압 코드에 기초하여 상기 다운 제어 코드를 생성하고, 상기 풀다운 제어 코드를 상기 풀다운 드라이버에 제공하는 제어/코드 생성 회로를 포함하는 임피던스 캘리브레이션 회로. |