| 번호 | 청구항 |

|---|---|

| 10 | 제1항에 있어서, 상기 입력 데이터는 커널 가중치(kernel weight)를 포함하고, 상기 PIM 어레이는 입력 특성 맵(input feature map)을 포함하는, PIM 장치. |

| 9 | 제1항에 있어서, 상기 연산 조건은 상기 신경망 어레이의 레이어의 사이즈, 상기 레이어의 깊이(depth), 입, 출력 채널의 개수, 커널 사이즈, 및 이미지 사이즈 중 적어도 하나를 포함하는 레이어 정보;상기 PIM 어레이의 사이즈; 및 상기 연산에 사용할 다중 비트들의 개수중 적어도 하나를 포함하는, PIM 장치. |

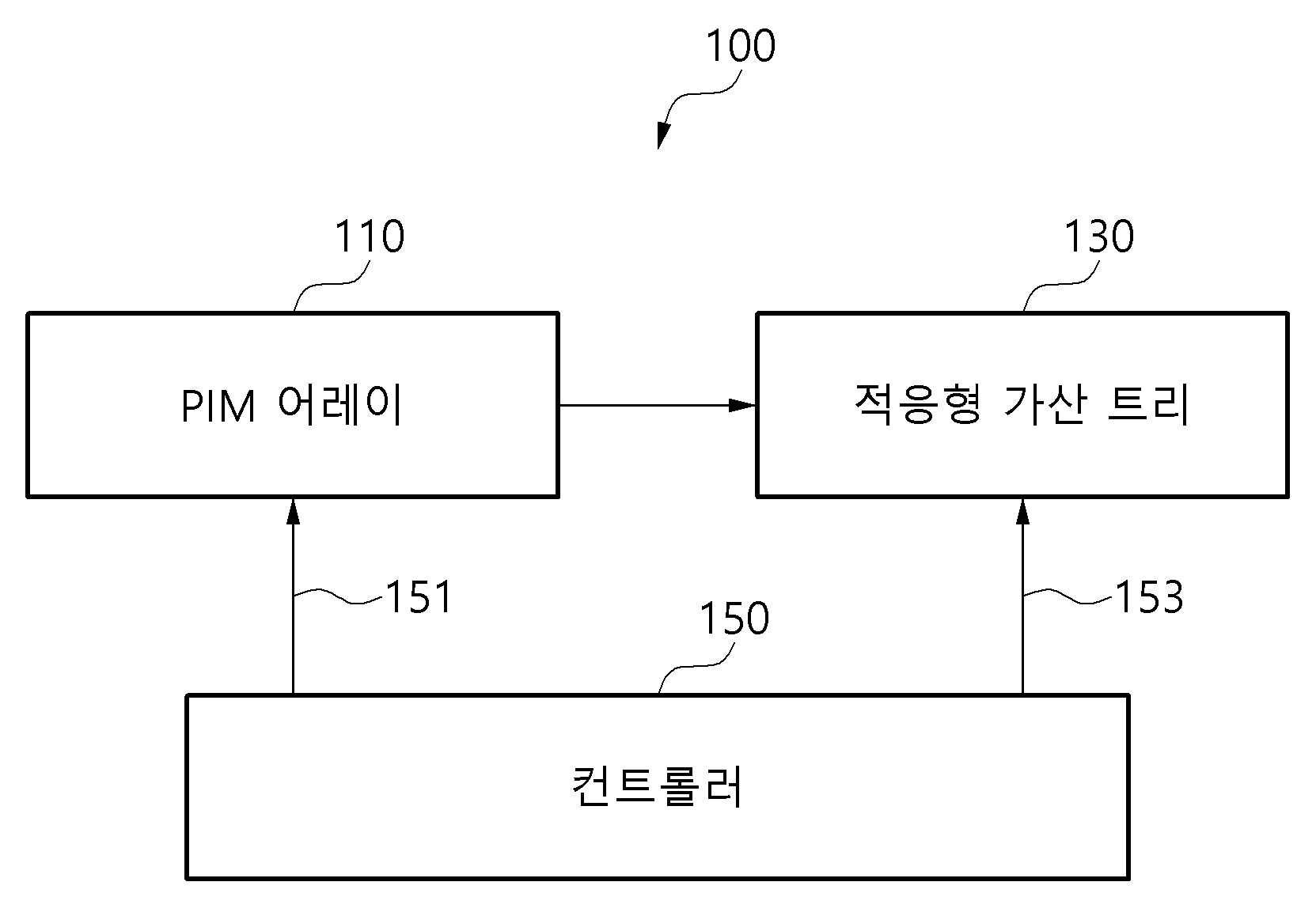

| 1 | 복수의 메모리 셀들을 포함하는 PIM(Processing In Memory) 어레이;연산 조건을 기초로, 상기 PIM 어레이에 대한 입력 데이터의 인가 유형들 및 상기 PIM 어레이에 대한 신경망 어레이의 다중 비트의 맵핑 유형들의 조합에 의한 후보 맵핑 포맷들 중 어느 하나의 타겟 맵핑 포맷을 결정하고, 상기 타겟 맵핑 포맷에 따른 연산을 위한 제어 신호를 생성하는 컨트롤러; 및 상기 타겟 맵핑 포맷에 따라, 상기 PIM 어레이의 상기 연산 결과에 대한 선택적인 시프트 연산 및 덧셈 연산을 수행하는 적응형 가산 트리를 포함하는, PIM 장치. |

| 2 | 제1항에 있어서, 상기 적응형 가산 트리는 상기 제어 신호에 따라, 다단계의 스테이지(stage) 별로, 상기 PIM 어레이의 홀수 행들의 데이터에 대해 상기 덧셈 연산을 수행하는 전가산기(full adder, FA)들; 및 상기 PIM 어레이의 짝수 행들의 데이터에 대해 상기 시프트 연산을 선택적으로 수행하는 시프팅 로직(shifting logic)을 포함하는, PIM 장치. |

| 3 | 제2항에 있어서, 상기 컨트롤러는 상기 다단계의 스테이지에서 상기 전가산기들에 의해 상기 덧셈 연산이 수행되기 이전에 상기 시프팅 로직에 의해 상기 시프트 연산이 수행되도록 하는 상기 제어 신호를 생성하여 전송하는, PIM 장치. |

| 4 | 제2항에 있어서,상기 시프팅 로직은 상기 제어 신호에 따라, 상기 PIM 어레이의 짝수 행들 각각에 대한 상기 덧셈 연산이 상기 전가산기에 의해 수행되기 이전에 상기 시프트 연산에 의해 상기 다중 비트의 가중치를 상기 PIM 어레이의 짝수 행들에 반영하는, PIM 장치. |

| 5 | 제1항에 있어서, 상기 컨트롤러는 상기 후보 맵핑 포맷들 각각에 대응하는 컴퓨팅 사이클을 산출하고,상기 컴퓨팅 사이클을 기초로, 상기 후보 맵핑 포맷들 중 상기 타겟 맵핑 포맷을 결정하는, PIM 장치. |

| 6 | 제5항에 있어서, 상기 컨트롤러는 상기 신경망 어레이의 다중 비트를 상기 PIM 어레이의 행 방향으로 맵핑하는 데 소요되는 사이클 수(AR cycle), 상기 다중 비트를 상기 PIM 어레이의 열 방향으로 맵핑하는 데 소요되는 사이클 수(AC cycle), 및 입력 포트를 통해 상기 입력 데이터가 인가 되는 횟수를 기초로, 상기 후보 맵핑 포맷들 각각에 대응하여 상기 컴퓨팅 사이클을 산출하는, PIM 장치. |

| 7 | 제1항에 있어서, 상기 컨트롤러는상기 후보 맵핑 포맷들 별로, 상기 선택적인 시프트 연산을 수행하는 시프팅 로직 및 상기 덧셈 연산을 수행하는 전가산기에 대한 설정 정보를 포함하는 룩-업 테이블(Look Up Table; LUT)을 더 포함하고,상기 룩-업 테이블을 이용하여, 상기 타겟 맵핑 포맷에 대응하는 상기 제어 신호를 생성하는, PIM 장치. |

| 8 | 제1항에 있어서, 상기 컨트롤러는 호스트 장치에서 상기 연산 조건에 따라 결정된 상기 타겟 맵핑 포맷에 대한 정보를 수신하고, 상기 타겟 맵핑 포맷에 대한 정보에 따라 상기 연산을 수행하기 위한 상기 제어 신호를 생성하는, PIM 장치. |

| 11 | 제1항에 있어서, 상기 컨트롤러는 상기 다중 비트를 상기 타겟 맵핑 포맷에 따른 다양한 형태의 비트 구조로 분할하여 상기 PIM 어레이에 맵핑하기 위한 상기 제어 신호를 생성하는, PIM 장치. |

| 12 | 제1항에 있어서, 상기 입력 데이터의 인가 유형들은 상기 입력 데이터를 입력 포트에 직렬로 인가하는 제1 인가 유형; 및 상기 입력 데이터를 상기 입력 포트에 병렬로 인가하는 제2 인가 유형을 포함하는, PIM 장치. |

| 13 | 제1항에 있어서, 상기 맵핑 유형들은 상기 다중 비트를 상기 PIM 어레이에 행(row) 별로 맵핑하는 제1 맵핑 유형;상기 다중 비트를 상기 PIM 어레이에 열(column) 별로 맵핑하는 제2 맵핑 유형; 및 상기 다중 비트를 상기 PIM 어레이에 분할하여 맵핑하는 제3 맵핑 유형 중 적어도 하나를 포함하는, PIM 장치. |

| 14 | 연산 조건을 수신하는 단계;상기 연산 조건을 기초로, PIM 어레이에 대한 입력 데이터의 인가 유형들 및 상기 PIM 어레이에 대한 신경망 어레이의 다중 비트의 맵핑 유형들의 조합에 의한 후보 맵핑 포맷들을 생성하는 단계;상기 후보 맵핑 포맷들 각각에 대응하는 컴퓨팅 사이클을 산출하는 단계;상기 컴퓨팅 사이클을 기초로, 상기 후보 맵핑 포맷들 중 어느 하나의 타겟 맵핑 포맷을 결정하는 단계; 및 상기 타겟 맵핑 포맷에 따른 연산을 위한 제어 신호를 생성하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 15 | 제14항에 있어서, 상기 컴퓨팅 사이클을 산출하는 단계는상기 신경망 어레이의 다중 비트를 상기 PIM 어레이의 행 방향으로 맵핑하는 데 소요되는 사이클 수(AR cycle), 상기 다중 비트를 상기 PIM 어레이의 열 방향으로 맵핑하는 데 소요되는 사이클 수(AC cycle), 및 입력 포트를 통해 상기 입력 데이터가 인가 되는 횟수를 기초로, 상기 후보 맵핑 포맷들 각각에 대응하여 상기 컴퓨팅 사이클을 산출하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 16 | 제14항에 있어서, 상기 제어 신호를 생성하는 단계는상기 후보 맵핑 포맷들 별로, 선택적인 시프트 연산을 수행하는 시프팅 로직 및 덧셈 연산을 수행하는 전가산기에 대한 설정 정보를 포함하는 룩-업 테이블(Look Up Table; LUT)을 이용하여, 상기 타겟 맵핑 포맷에 대응하는 상기 PIM 어레이의 맵핑 유형과 상기 입력 데이터의 인가 형태를 지원하기 위한 상기 제어 신호를 생성하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 17 | 제14항에 있어서, 상기 제어 신호를 생성하는 단계는상기 타겟 맵핑 포맷에 따라, 상기 PIM 어레이의 상기 연산 결과에 대한 선택적인 시프트 연산 및 덧셈 연산을 수행하기 위한 제어 신호를 생성하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 18 | 제17항에 있어서, 상기 제어 신호를 생성하는 단계는다단계의 스테이지에서 전가산기들에 의해 상기 덧셈 연산이 수행되기 이전에 시프팅 로직에 의해 상기 시프트 연산이 수행되도록 하는 상기 제어 신호를 생성하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 19 | 제14항에 있어서, 상기 제어 신호를 생성하는 단계는상기 다중 비트를 상기 타겟 맵핑 포맷에 따른 다양한 형태의 비트 구조로 분할하여 상기 PIM 어레이에 맵핑하기 위한 상기 제어 신호를 생성하는 단계를 포함하는, PIM 장치의 동작 방법. |

| 20 | 제14항에 있어서, 상기 연산 조건은 상기 신경망 어레이의 레이어의 사이즈, 상기 레이어의 깊이(depth), 입, 출력 채널의 개수, 커널 사이즈, 및 이미지 사이즈 중 적어도 하나를 포함하는 레이어 정보;상기 PIM 어레이의 사이즈; 및 상기 연산에 사용할 다중 비트들의 개수중 적어도 하나를 포함하는, PIM 장치의 동작 방법. |