| 번호 | 청구항 |

|---|---|

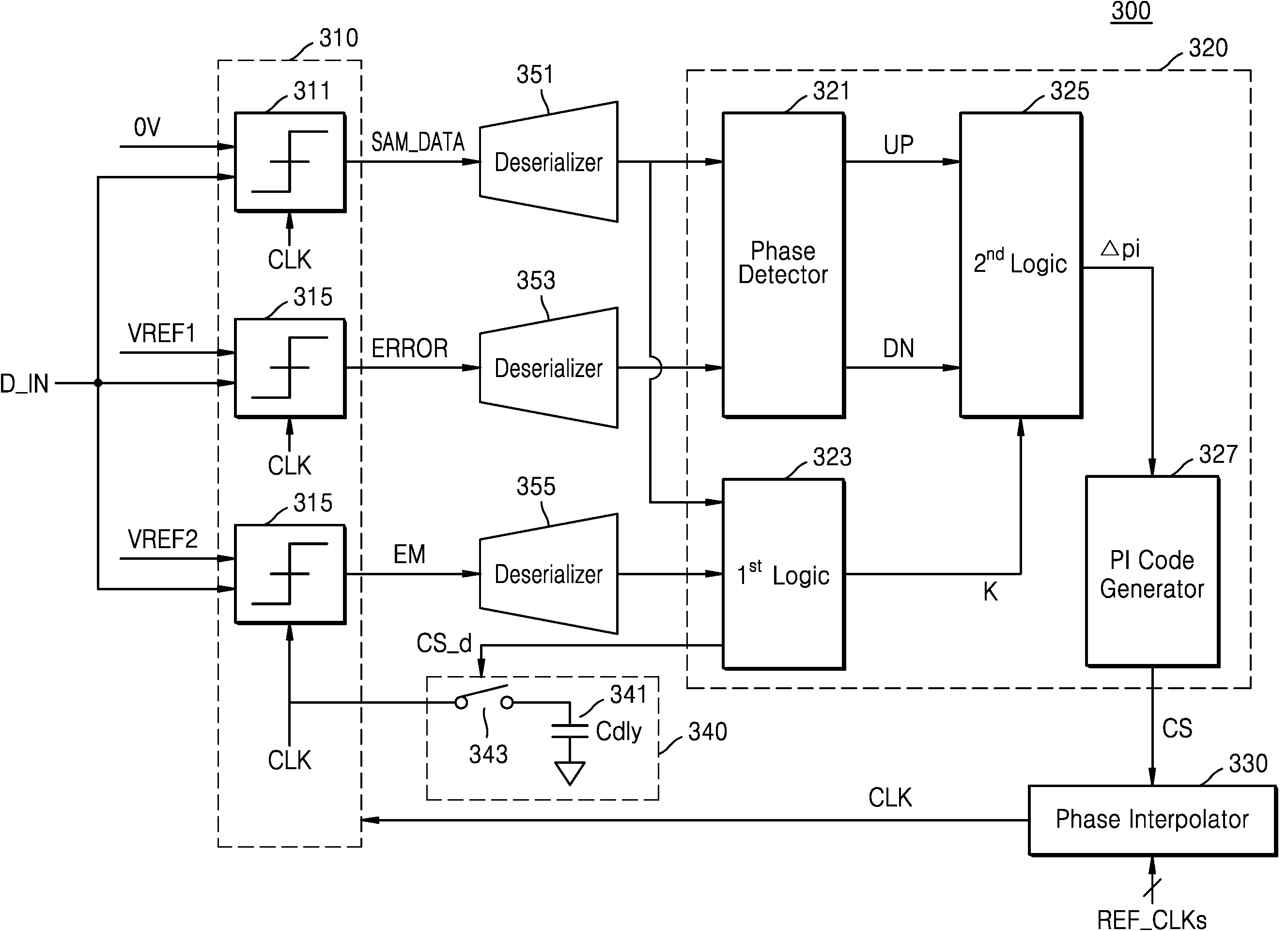

| 1 | 입력 데이터 신호와 다수의 기준 전압의 비교 결과 또는 상기 입력 데이터 신호를 복원 클록 신호에 따라 샘플링하는 샘플러; 및K 신호, 업 신호 및 다운 신호에 기초하여 상기 복원 클록 신호의 위상을 제어하는 제어 신호를 출력하는 제어 회로를 포함하며,상기 샘플러는,상기 복원 클록 신호의 엣지에서 상기 입력 데이터 신호를 샘플링하여 데이터 샘플 신호를 출력하는 제1 샘플러;상기 복원 클록 신호의 엣지에서 상기 입력 데이터 신호의 전압 레벨을 제1 기준 전압과 비교하여 에러 신호를 출력하는 제2 샘플러; 및상기 복원 클록 신호의 엣지 또는 지연된 복원 클록 신호의 엣지에서 상기 입력 데이터 신호의 전압 레벨을 제2 기준 전압과 비교하여 아이 모니터링 신호를 출력하는 제3 샘플러를 포함하며,상기 제어 회로는,상기 데이터 샘플 신호 및 상기 에러 신호에 기초하여 상기 업 신호 또는 상기 다운 신호를 출력하는 위상 검출기;상기 데이터 샘플 신호 및 상기 아이 모니터링 신호에 기초하여 상기 K 신호를 출력하는 제1 로직;상기 K 신호, 상기 업 신호 및 상기 다운 신호에 기초하여 위상 오차 신호를 출력하는 제2 로직; 및상기 위상 오차 신호에 기초하여 상기 제어 신호를 출력하는 PI 코드 발생기를 포함하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 2 | 제1 항에 있어서,상기 K 신호는 상기 업 신호와 상기 다운 신호의 비율을 조절하는 K의 값을 나타내는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 3 | 제1 항에 있어서,상기 위상 오차 신호는, 수학식 △pi= K * DN - UP에 따른 신호이며,△pi는 상기 위상 오차 신호의 값을 나타내며, DN은 상기 다운 신호의 값을 나타내며, UP는 상기 업 신호의 값을 나타내며, K는 상기 업 신호와 다운 신호의 비율을 조절하는 파라미터를 나타내는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 4 | 제1 항에 있어서,상기 제어 회로의 지연 회로 제어 신호에 응답하여 상기 제3 샘플러에게 상기 복원 클록 신호 또는 상기 지연된 복원 클록 신호를 제공하는 지연 회로를 더 포함하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 5 | 제4 항에 있어서,상기 제어 회로는, 상기 지연 회로에게 상기 지연 회로 제어 신호를 출력함으로써, 주기적으로 상기 복원 클록을 디더링하고,상기 제2 기준 전압에 대응하는 제2 데이터 레벨 신호 값의 증감 여부를 식별하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 6 | 제1 항에 있어서,상기 데이터 샘플 신호의 3개의 순차적인 데이터 샘플들(Dn-1, Dn, Dn+1)의 값이 (-1, 1, -1)인 경우,상기 제1 로직은 상기 제2 기준 전압에 대응하는 제2 데이터 레벨 신호를 출력하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 7 | 제1 항에 있어서,상기 지연된 복원 클록 신호가 상기 제3 샘플러에 인가되고, 상기 제2 기준 전압에 대응하는 제2 데이터 레벨 신호 값이 증가한 경우,상기 제1 로직은 상기 K 신호의 값인 K가 감소하도록 K의 값을 조절하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 8 | 제1 항에 있어서,상기 제2 기준 전압의 전압 레벨은 상기 복원 클록의 락킹 포인트에서의 아이 하이트의 값과 비례하는 것을 특징으로 하는, 클록 데이터 복원 회로. |

| 9 | 수신 회로; 및채널을 통해 입력 데이터 신호를 상기 수신 회로에 송신하도록 구성된 송신 회로를 포함하고,상기 수신 회로는,상기 입력 데이터 신호와 다수의 기준 전압의 비교 결과 또는 상기 입력 데이터 신호를 복원 클록 신호에 따라 샘플링하는 샘플러; 및K 신호, 업 신호 및 다운 신호에 기초하여 상기 복원 클록 신호의 위상을 제어하는 제어 신호를 출력하는 제어 회로를 포함하며,상기 샘플러는,상기 복원 클록 신호의 엣지에서 상기 입력 데이터 신호를 샘플링하여 데이터 샘플 신호를 출력하는 제1 샘플러;상기 복원 클록 신호의 엣지에서 상기 입력 데이터 신호의 전압 레벨을 제1 기준 전압과 비교하여 에러 신호를 출력하는 제2 샘플러; 및상기 복원 클록 신호의 엣지 또는 지연된 복원 클록 신호의 엣지에서 상기 입력 데이터 신호의 전압 레벨을 제2 기준 전압과 비교하여 아이 모니터링 신호를 출력하는 제3 샘플러를 포함하며,상기 제어 회로는,상기 데이터 샘플 신호 및 상기 에러 신호에 기초하여 상기 업 신호 또는 상기 다운 신호를 출력하는 위상 검출기;상기 데이터 샘플 신호 및 상기 아이 모니터링 신호에 기초하여 상기 K 신호를 출력하는 제1 로직;상기 K 신호, 상기 업 신호 및 상기 다운 신호에 기초하여 위상 오차 신호를 출력하는 제2 로직; 및상기 위상 오차 신호에 기초하여 상기 제어 신호를 출력하는 PI 코드 발생기를 포함하는 것을 특징으로 하는, 장치. |

| 10 | 위상 검출기에 있어서,데이터 샘플 신호 및 에러 신호에 기초하여 업 신호 또는 다운 신호를 출력하는 위상 검출 로직;상기 데이터 샘플 신호 및 아이 모니터링 신호에 기초하여 K 신호를 출력하는 제1 로직; 및상기 K 신호, 상기 업 신호 및 상기 다운 신호에 기초하여 위상 오차 신호를 출력하는 제2 로직을 포함하는 위상 검출기. |