| 번호 | 청구항 |

|---|---|

| 3 | 제2 항에 있어서,상기 제1 컨트롤러는,상기 제1 DCDL의 딜레이를 증가시킬 때, 상기 제1 DCDL의 딜레이가 상기 제1 DCDL의 최대 딜레이에 도달한 경우, 상기 제1 DCDL의 딜레이를 상기 제1 DCDL의 최대 딜레이에서 상기 제1 DCDL의 최소 딜레이로 변경하도록 구성된 것을 특징으로 하는 주파수 체배기. |

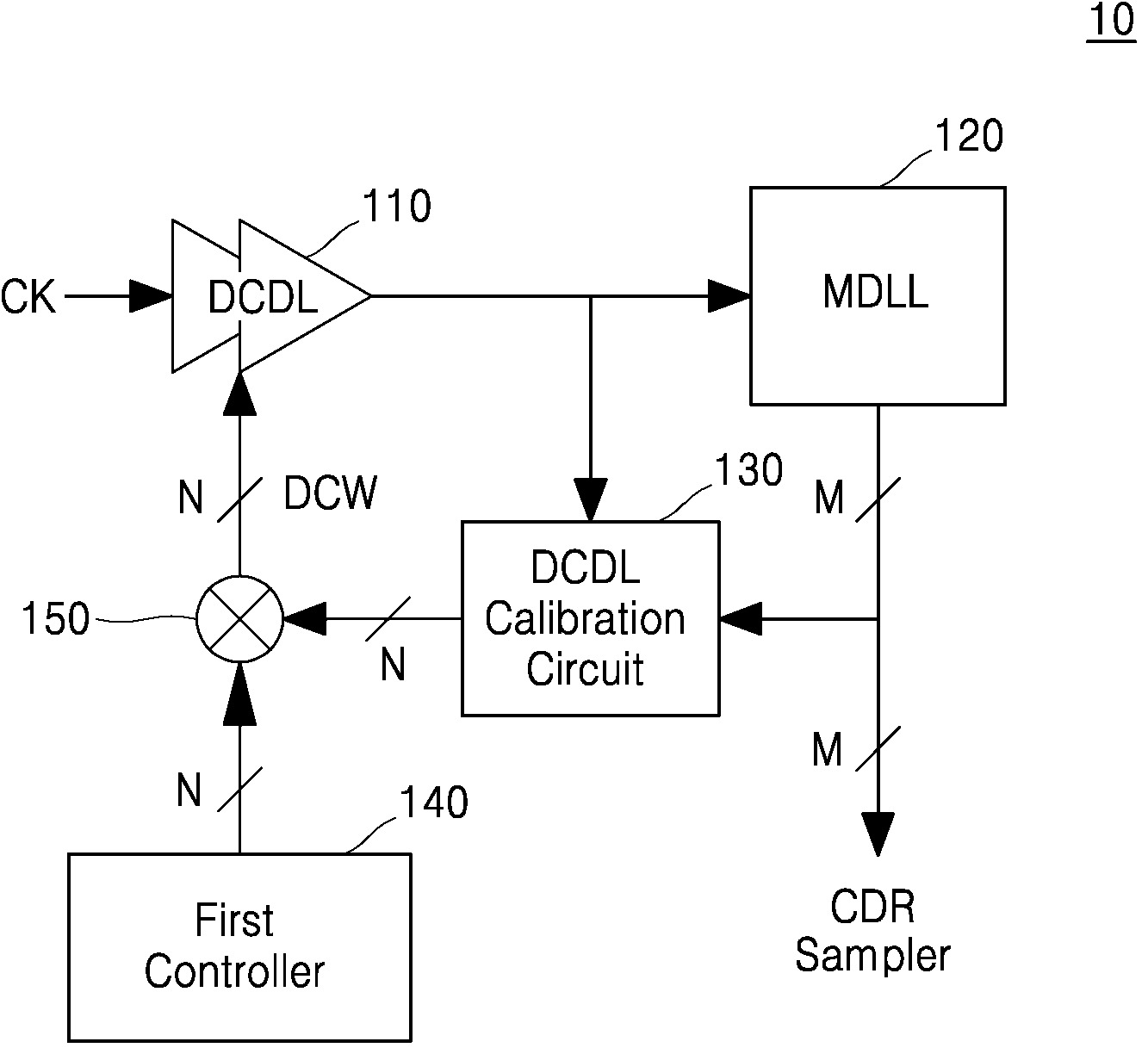

| 1 | 제1 클럭 신호를 수신하고, 상기 제1 클럭 신호의 위상을 변경하여 제2 클럭 신호를 생성하도록 구성된 제1 DCDL(Digitally Controlled Delay Line);상기 제2 클럭 신호의 주파수를 체배하여 제3 클럭 신호를 생성하도록 구성된 구성된 MDLL(Multiplying Delay-Locked Loop); 및상기 제2 클럭 신호를 수신하고, 상기 제1 DCDL의 최대 딜레이와 최소 딜레이의 차이가 상기 제3 클럭 신호의 주기와 일치하도록 상기 제1 DCDL의 게인(gain)을 조정하는 게인 신호를 생성하도록 구성된 DCDL 조정 회로(DCDL calibration circuit)를 포함하는 주파수 체배기. |

| 2 | 제1 항에 있어서,상기 제1 DCDL의 딜레이 및 상기 MDLL의 주파수 체배 비율(frequency multiplication ratio)을 제어하도록 구성된 제1 컨트롤러를 더 포함하는 것을 특징으로 하는 주파수 체배기. |

| 4 | 제2 항에 있어서,상기 제1 컨트롤러는,상기 제1 DCDL의 딜레이를 증가시킬 때, 상기 제1 DCDL의 딜레이가 상기 제1 DCDL의 최대 딜레이에 도달한 경우, 상기 MDLL의 주파수 체배 비율을 1만큼 감소시키도록 구성된 것을 특징으로 하는 주파수 체배기. |

| 5 | 제2 항에 있어서,상기 제1 컨트롤러는,상기 제1 DCDL의 딜레이를 감소시킬 때, 상기 제1 DCDL의 딜레이가 상기 제1 DCDL의 최소 딜레이에 도달한 경우, 상기 제1 DCDL의 딜레이를 상기 제1 DCDL의 최소 딜레이에서 상기 제1 DCDL의 최대 딜레이로 변경하도록 구성된 것을 특징으로 하는 주파수 체배기. |

| 6 | 제2 항에 있어서,상기 제1 컨트롤러는,상기 제1 DCDL의 딜레이를 감소시킬 때, 상기 제1 DCDL의 딜레이가 상기 제1 DCDL의 최소 딜레이에 도달한 경우, 상기 MDLL의 주파수 체배 비율을 1만큼 증가시키도록 구성된 것을 특징으로 하는 주파수 체배기. |

| 7 | 제1 항에 있어서,상기 DCDL 조정 회로는,상기 제2 클럭 신호의 위상을 변경하여 제4 클럭 신호를 생성하도록 구성된 제2 DCDL;상기 제4 클럭 신호의 위상을 변경하여 제5 클럭 신호를 생성하도록 구성된 제3 DCDL;상기 제3 클럭 신호 및 상기 제5 클럭 신호의 위상차를 검출하도록 구성된 BBPD(Bang Bang Phase Detector); 및상기 제3 클럭 신호 및 상기 제5 클럭 신호의 위상차에 기초하여 상기 제1 DCDL의 게인을 조정하는 상기 게인 신호를 생성하도록 구성된 제2 컨트롤러를 포함하는 것을 특징으로 하는 주파수 체배기. |

| 8 | 제7 항에 있어서,상기 제2 컨트롤러는,상기 제2 DCDL의 딜레이를 상기 제2 DCDL의 최소 딜레이로 변경하고,상기 BBPD의 출력 신호에 기초하여 상기 제3 클럭 신호와 상기 제4 클럭 신호 사이의 위상 오프셋(phase offset)을 검출하고,상기 위상 오프셋에 기초하여 상기 제3 DCDL의 딜레이를 변경함으로써, 상기 제3 클럭 신호와 상기 제5 클럭 신호의 위상을 일치시키도록 구성된 것을 특징으로 하는 주파수 체배기. |

| 9 | 제7 항에 있어서,상기 제2 컨트롤러는,상기 제2 DCDL의 딜레이를 상기 제2 DCDL의 최대 딜레이로 변경하고,상기 BBPD의 출력 신호에 기초하여 제3 클럭 신호와 상기 제5 클럭 신호의 위상차를 검출하고,상기 제3 클럭 신호와 상기 제5 클럭 신호의 위상차에 기초하여 상기 제1 DCDL의 게인을 변경함으로써, 상기 제3 클럭 신호와 상기 제5 클럭 신호의 위상을 일치시키도록 구성된 것을 특징으로 하는 주파수 체배기. |

| 10 | 제9 항에 있어서,상기 제2 컨트롤러는,상기 제5 클럭 신호의 위상이 상기 제3 클럭 신호의 위상보다 큰 경우, 상기 제1 DCDL의 게인을 감소시키도록 구성된 것을 특징으로 하는 주파수 체배기. |