| 번호 | 청구항 |

|---|---|

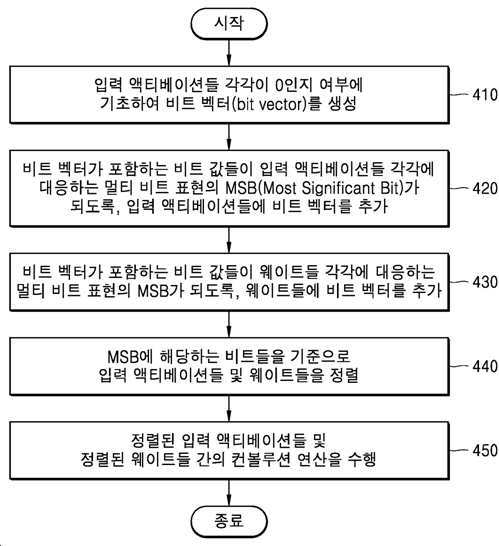

| 1 | 뉴럴 네트워크에서 입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법에 있어서, 상기 입력 액티베이션들 각각이 0인지 여부에 기초하여 비트 벡터(bit vector)를 생성하는 단계; 상기 비트 벡터가 포함하는 비트 값들이 상기 입력 액티베이션들 각각에 대응하는 멀티 비트 표현의 MSB(Most Significant Bit)가 되도록, 상기 입력 액티베이션들에 상기 비트 벡터를 추가하는 단계; 상기 비트 벡터가 포함하는 비트 값들이 상기 웨이트들 각각에 대응하는 멀티 비트 표현의 MSB가 되도록, 상기 웨이트들에 상기 비트 벡터를 추가하는 단계; 상기 MSB에 해당하는 비트들을 기준으로 상기 입력 액티베이션들 및 상기 웨이트들을 정렬하는 단계; 및상기 정렬된 입력 액티베이션들 및 상기 정렬된 웨이트들 간의 연산을 수행하는 단계를 포함하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 2 | 제 1 항에 있어서, 상기 비트 벡터를 생성하는 단계는,상기 입력 액티베이션들 중 0에 해당하지 않는 입력 액티베이션들에 대응하여 제 1 비트 값을 생성하고, 상기 입력 액티베이션들 중 0에 해당하는 입력 액티베이션들에 대응하여 제 2 비트 값을 생성하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 3 | 제 2 항에 있어서, 상기 정렬하는 단계는, 상기 입력 액티베이션들을 MSB에 상기 제 1 비트 값이 추가된 입력 엑티베이션들이 포함된 제 1 그룹 및 MSB에 상기 제 2 비트 값이 추가된 입력 엑티베이션들이 포함된 제 2 그룹의 순서로 정렬하는 단계; 및 상기 웨이트들을 MSB에 상기 제 1 비트 값이 추가된 웨이트들이 포함된 제 3 그룹 및 MSB에 상기 제 2 비트 값이 추가된 웨이트들이 포함된 제 4 그룹의 순서로 정렬하는 단계를 더 포함하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 4 | 제 3 항에 있어서, 상기 연산을 수행하는 단계는, 상기 제 2 그룹에 포함된 입력 액티베이션들의 개수가 기 설정된 값 미만인 경우에는, 상기 정렬된 입력 액티베이션들 중 n 번째(n은 자연수) 입력 액티베이션 및 상기 정렬된 웨이트들 중 n 번째 웨이트 간의 연산 각각을 수행하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 5 | 제 3 항에 있어서, 상기 연산을 수행하는 단계는, 상기 제 2 그룹에 포함된 입력 액티베이션들의 개수가 기 설정된 값 이상인 경우에는, 상기 제 1 그룹에 포함된 입력 액티베이션들 및 상기 제 3 그룹에 포함된 웨이트들 간의 연산을 수행하고,상기 제 2 그룹에 포함된 입력 액티베이션들 및 상기 제 4 그룹에 포함된 웨이트들 간의 연산의 적어도 일부를 스킵하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 6 | 제 5 항에 있어서, 상기 기 설정된 값은 상기 연산이 동시에 수행될 수 있는 입력 액티베이션들의 총 개수에 해당하고, 상기 제 2 그룹에 포함된 입력 액티베이션들 중 기 설정된 값에 해당하는 개수의 입력 액티베이션들 및 상기 제 4 그룹에 포함된 웨이트들 중 기 설정된 값에 해당하는 개수의 웨이트들 간의 연산을 스킵하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 7 | 제 1 항에 있어서, 상기 비트 벡터를 생성하는 단계는,상기 입력 액티베이션들 중 0에 해당하지 않는 입력 액티베이션들에 대응하여 제 1 비트 값을 생성하고, 상기 입력 액티베이션들 중 0에 해당하는 입력 액티베이션들에 대응하여 제 2 비트 값을 생성하여 제 1 벡터를 생성하는 단계; 상기 웨이트들 중 0에 해당하지 않는 웨이트들에 대응하여 제 1 비트 값을 생성하고, 상기 웨이트들 중 0에 해당하는 웨이트들에 대응하여 제 2 비트 값을 생성하여 제 2 벡터를 생성하는 단계; 및상기 제 1 벡터 및 상기 제 2 벡터 간의 AND 논리 연산을 수행하여 상기 비트 벡터를 생성하는 단계를 더 포함하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 8 | 제 1 항에 있어서, 상기 웨이트들을 정렬하는 단계는, 상기 입력 액티베이션들 중 제 1 입력 액티베이션에 대응하는 멀티 비트 표현의 MSB에 추가된 비트 값을, 상기 웨이트들 중 상기 제 1 입력 액티베이션과 연산이 수행될 제 1 웨이트에 대응하는 멀티 비트 표현의 MSB에 추가하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 9 | 제 1 항에 있어서, 상기 정렬하는 단계는, 상기 입력 액티베이션들 및 상기 웨이트들을 거품 정렬(bubble sort) 알고리즘, 셀 정렬(shell sort) 알고리즘, 바이토닉 정렬(bitonic sort) 알고리즘, 빗질 정렬(comb sort) 알고리즘, 사이클 정렬(cycle sort) 알고리즘 및 홀-짝 정렬(Even-odd mergesort) 알고리즘 중 어느 하나에 기초하여 정렬하는,입력 액티베이션들 및 웨이트들 간 연산을 수행하는 방법. |

| 10 | 제 1항 내지 제 9항 중 어느 한 항의 방법을 실행하는 명령어들을 포함하는 하나 이상의 프로그램이 기록된 컴퓨터로 읽을 수 있는 기록매체. |

| 11 | 뉴럴 네트워크를 실시(implement)하는 장치에 있어서, 메모리; 및입력 액티베이션들 및 웨이트들 간 컨볼루션 연산을 수행하는 프로세서를 포함하고,상기 프로세서는, 상기 입력 액티베이션들 각각이 0인지 여부에 기초하여 비트 벡터(bit vector)를 생성하고, 상기 비트 벡터가 포함하는 비트 값들이 상기 입력 액티베이션들 각각에 대응하는 멀티 비트 표현의 MSB(Most Significant Bit)가 되도록, 상기 입력 액티베이션들에 상기 비트 벡터를 추가하고, 상기 비트 벡터가 포함하는 비트 값들이 상기 웨이트들 각각에 대응하는 멀티 비트 표현의 MSB가 되도록, 상기 웨이트들에 상기 비트 벡터를 추가하고, 상기 MSB에 해당하는 비트들을 기준으로 상기 입력 액티베이션들 및 상기 웨이트들을 정렬하고, 상기 정렬된 입력 액티베이션들 및 상기 정렬된 웨이트들 간의 연산을 수행하는,뉴럴 네트워크를 실시하는 장치. |

| 12 | 제 11 항에 있어서, 상기 프로세서는, 상기 입력 액티베이션들 중 0에 해당하지 않는 입력 액티베이션들에 대응하여 제 1 비트를 생성하고, 상기 입력 액티베이션들 중 0에 해당하는 입력 액티베이션들에 대응하여 제 2 비트를 생성하는,뉴럴 네트워크를 실시하는 장치. |

| 13 | 제 12 항에 있어서, 상기 프로세서는, 상기 입력 액티베이션들을 MSB에 상기 제 1 비트가 추가된 입력 엑티베이션들이 포함된 제 1 그룹 및 MSB에 상기 제 2 비트가 추가된 입력 엑티베이션들이 포함된 제 2 그룹의 순서로 정렬하고, 상기 웨이트들을 MSB에 상기 제 1 비트가 추가된 웨이트들이 포함된 제 3 그룹 및 MSB에 상기 제 2 비트가 추가된 웨이트들이 포함된 제 4 그룹의 순서로 정렬하는,뉴럴 네트워크를 실시하는 장치. |

| 14 | 제 13 항에 있어서, 상기 프로세서는, 상기 제 2 그룹에 포함된 입력 액티베이션들의 개수가 기 설정된 값 미만인 경우에는, 상기 정렬된 입력 액티베이션들 중 n 번째(n은 자연수) 입력 액티베이션 및 상기 정렬된 웨이트들 중 n 번째 웨이트 간의 연산 각각을 수행하는,뉴럴 네트워크를 실시하는 장치. |

| 15 | 제 13 항에 있어서, 상기 프로세서는,상기 제 2 그룹에 포함된 입력 액티베이션들의 개수가 기 설정된 값 이상인 경우에는, 상기 제 1 그룹에 포함된 입력 액티베이션들 및 상기 제 3 그룹에 포함된 웨이트들 간의 연산을 수행하고,상기 제 2 그룹에 포함된 입력 액티베이션들 및 상기 제 4 그룹에 포함된 웨이트들 간의 연산의 적어도 일부를 스킵하는,뉴럴 네트워크를 실시하는 장치. |

| 16 | 제 15 항에 있어서, 상기 기 설정된 값은 상기 연산이 동시에 수행될 수 있는 입력 액티베이션들의 총 개수에 해당하고, 상기 프로세서는,상기 제 2 그룹에 포함된 입력 액티베이션들 중 기 설정된 값에 해당하는 개수의 입력 액티베이션들 및 상기 제 4 그룹에 포함된 웨이트들 중 기 설정된 값에 해당하는 개수의 웨이트들 간의 연산을 스킵하는,뉴럴 네트워크를 실시하는 장치. |

| 17 | 제 11 항에 있어서,상기 프로세서는,상기 입력 액티베이션들 중 0에 해당하지 않는 입력 액티베이션들에 대응하여 제 1 비트를 생성하고, 상기 입력 액티베이션들 중 0에 해당하는 입력 액티베이션들에 대응하여 제 2 비트를 생성하여 제 1 벡터를 생성하고,상기 웨이트들 중 0에 해당하지 않는 웨이트들에 대응하여 제 1 비트를 생성하고, 상기 웨이트들 중 0에 해당하는 웨이트들에 대응하여 제 2 비트를 생성하여 제 2 벡터를 생성하고,상기 제 1 벡터 및 상기 제 2 벡터 간의 AND 논리 연산을 수행하여 상기 비트 벡터를 생성하는,뉴럴 네트워크를 실시하는 장치. |

| 18 | 제 11항에 있어서, 상기 프로세서는, 상기 입력 액티베이션들 중 제 1 입력 액티베이션에 대응하는 멀티 비트 표현의 MSB에 추가된 비트 값을, 상기 웨이트들 중 상기 제 1 입력 액티베이션과 연산이 수행될 제 1 웨이트에 대응하는 멀티 비트 표현의 MSB에 추가하는,뉴럴 네트워크를 실시하는 장치. |

| 19 | 제 11 항에 있어서,상기 프로세서는, 상기 입력 액티베이션들 및 상기 웨이트들을 거품 정렬(bubble sort) 알고리즘, 셀 정렬(shell sort) 알고리즘, 바이토닉 정렬(bitonic sort) 알고리즘, 빗질 정렬(comb sort) 알고리즘, 사이클 정렬(cycle sort) 알고리즘 및 홀-짝 정렬(Even-odd mergesort) 알고리즘 중 어느 하나에 기초하여 정렬하는,뉴럴 네트워크를 실시하는 장치. |