| 번호 | 청구항 |

|---|---|

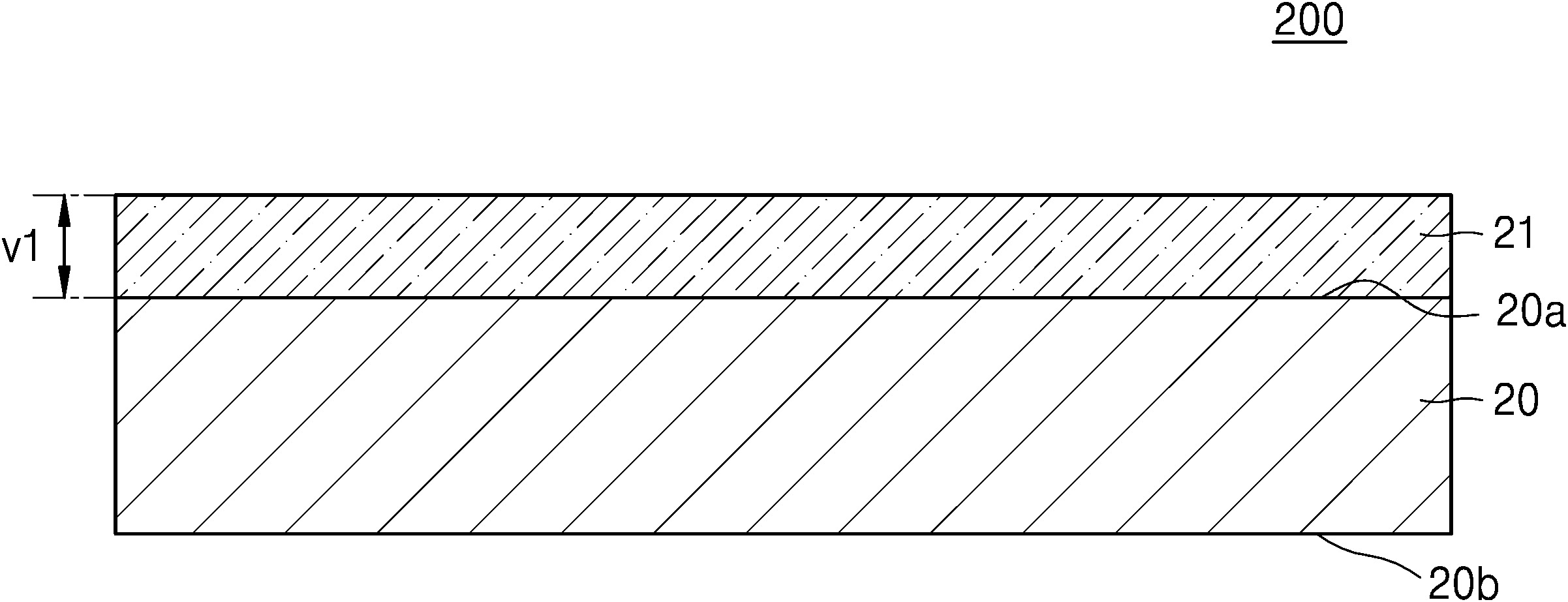

| 1 | 반도체 칩; 및상기 반도체 칩 상에 1 마이크로미터 내지 300 마이크로미터의 두께를 가지고, 상면이 외부에 노출된 폴리디메틸실록산(polydimethylsiloxane, PDMS) 층;을 포함하고,상기 폴리디메틸실록산 층의 하면은 상기 반도체 칩의 상면과 동일한 수직 레벨에 배치되는 것을 특징으로 하는,반도체 패키지. |

| 2 | 제1 항에 있어서,상기 폴리디메틸실록산 층의 측면은 상기 반도체 칩의 측면과 자기 정렬되고,상기 폴리디메틸실록산 층은 1 마이크로미터 내지 200 마이크로미터의 두께를 가지는 것을 특징으로 하는 반도체 패키지. |

| 3 | 제1 항에 있어서,상기 반도체 패키지는,상기 반도체 칩 상의 프라이머; 및상기 프라이머 상의 접착제;를 더 포함하고,상기 폴리디메틸실록산 층은 상기 프라이머 상에 있고,상기 접착제는 상기 폴리디메틸실록산 층에 매립된 것을 특징으로 하는 반도체 패키지. |

| 4 | 제1 항에 있어서,상기 폴리디메틸실록산 층은 요철 구조인 것을 특징으로 하는 반도체 패키지. |

| 5 | 반도체 칩;상기 반도체 칩 상의 히트 싱크; 및상기 히트 싱크 상에 1 마이크로미터 내지 300 마이크로미터의 두께를 가지고, 상면이 외부에 노출된 폴리디메틸실록산 층;을 포함하고,상기 히트 싱크의 하면은 상기 반도체 칩의 상면보다 큰 면적을 가지며 상기 히트 싱크는 상기 반도체 칩의 상면을 덮도록 배치되는 것을 특징으로 하는반도체 패키지. |

| 6 | 제5 항에 있어서,상기 히트 싱크의 측면은 상기 반도체 칩의 측면보다 내측에 있고,상기 폴리디메틸실록산 층의 측면은 상기 히트싱크의 측면과 자기 정렬되고,상기 폴리디메틸실록산 층은,1 마이크로미터 내지 200 마이크로미터의 두께를 가지는 것을 특징으로 하는 반도체 패키지. |

| 7 | 기판;상기 기판 상에 탑재된 반도체 칩;상기 기판 상에 탑재되고, 상기 반도체 칩을 제어하도록 구성된 컨트롤러;상기 반도체 칩 및 상기 컨트롤러를 감싸는 하우징; 및상기 하우징의 내벽 상의 내부 폴리디메틸실록산 층;을 포함하고,상기 내부 폴리디메틸실록산 층은 1 마이크로미터 내지 300 마이크로미터의 두께를 가지는 것을 특징으로 하는 반도체 장치. |

| 8 | 제7 항에 있어서,상기 반도체 장치는,상기 하우징의 외벽 상의 외부 폴리디메틸실록산 층;을 포함하고,상기 외부 폴리디메틸실록산 층은 1 마이크로미터 내지 300 마이크로미터의 두께를 가지는 것을 특징으로 하는 반도체 장치. |

| 9 | 제7 항에 있어서,상기 반도체 장치는,상기 컨트롤러 상에 있고, 상면이 외부에 노출된 제1 폴리디메틸실록산 층;을 더 포함하고,상기 제1 폴리디메틸실록산 층은 1 마이크로미터 내지 300 마이크로미터의 두께를 가지는 것을 특징으로 하는 반도체 장치. |

| 10 | 제9 항에 있어서,상기 반도체 장치는,상기 컨트롤러 및 상기 제1 폴리디메틸실록산 층 사이에 개재된 히트 싱크;를 더 포함하는 것을 특징으로 하는 반도체 장치. |