| 번호 | 청구항 |

|---|---|

| 18 | 제 13 항에 있어서, 상기 나노 패턴은 격자를 포함하며, 상기 격자는 상기 기판 상에 불규칙적으로 배열되는,전도체의 제조 방법. |

| 19 | 삭제 |

| 20 | 삭제 |

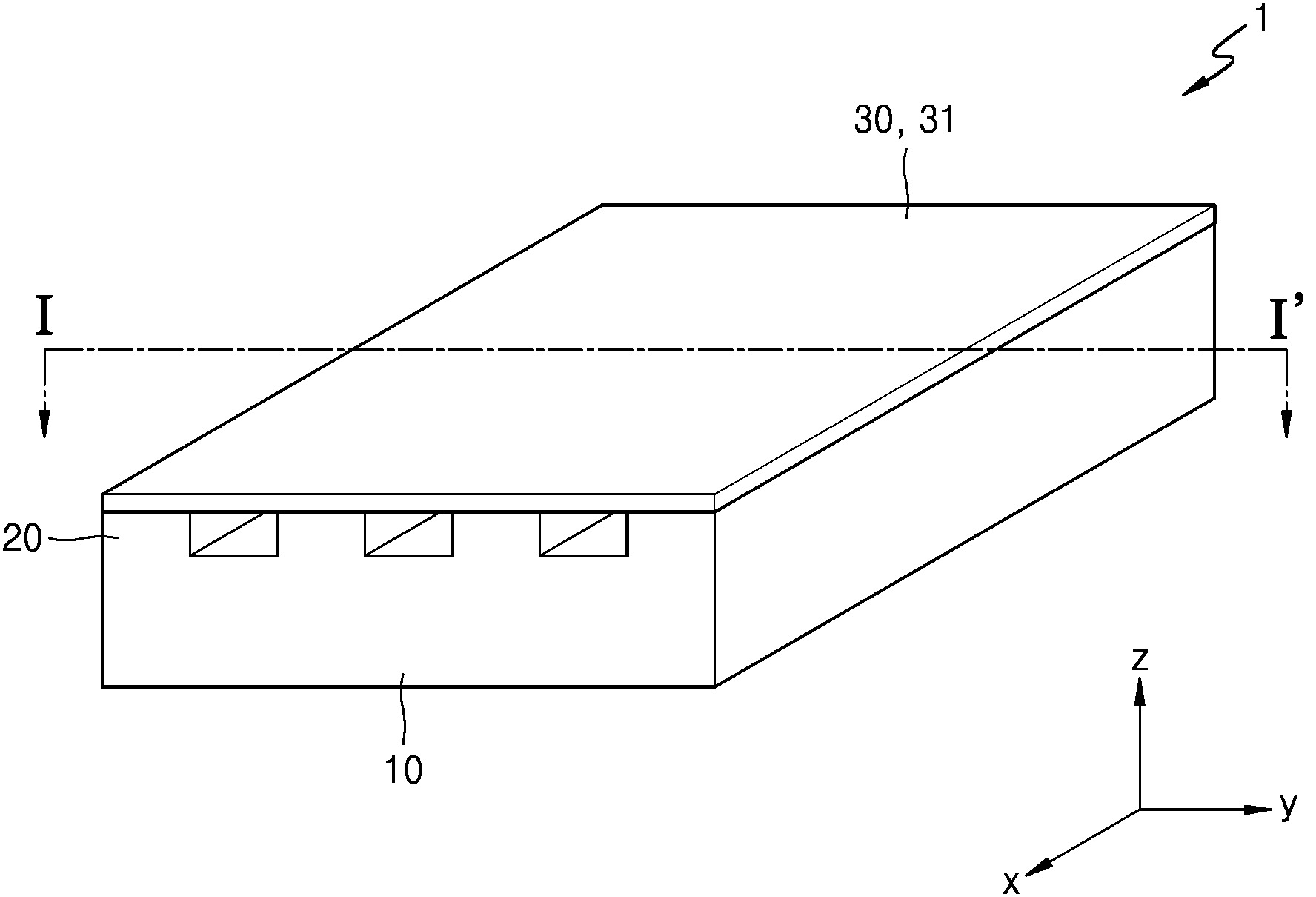

| 1 | 기판; 상기 기판의 상부에 배치되는 나노 패턴; 및상기 나노 패턴의 상부에 배치되는 그래핀 층;을 포함하며,상기 나노 패턴은 제1 패턴부 및 제2 패턴부를 포함하며, 상기 제1 및 제2 패턴부는 서로 교번하여 배치되고,상기 기판과 상기 제1 패턴부는 동일한 물질을 포함하며,상기 기판과 상기 제1 패턴부는 백금(Pt), 구리(Cu), 은(Ag) 또는 금(Au) 중 하나 이상을 포함하고, 상기 제2 패턴부는 니켈(Ni), 코발트(Co) 또는 티타늄(Ti) 중 하나 이상을 포함하는,전도체. |

| 2 | 제 1 항에 있어서, 상기 나노 패턴은 일 방향으로 연장되는 복수 개의 선형 구조를 포함하며, 상기 복수 개의 선형 구조는 소정의 간격을 사이에 두고 서로 이격되도록 배치되는,전도체. |

| 3 | 제 1 항에 있어서, 상기 나노 패턴은 복수 개의 격자를 포함하며, 상기 복수 개의 격자는 상기 기판 상에 규칙적으로 배열되는,전도체. |

| 4 | 제 1 항에 있어서, 상기 나노 패턴은 복수 개의 격자를 포함하며, 상기 복수 개의 격자는 상기 기판 상에 불규칙적으로 배열되는,전도체. |

| 5 | 삭제 |

| 6 | 삭제 |

| 7 | 삭제 |

| 8 | 삭제 |

| 9 | 삭제 |

| 10 | 삭제 |

| 11 | 기판; 상기 기판의 상부에 배치되는 나노 패턴; 및상기 나노 패턴의 상부에 배치되는 2차원 물질층;을 포함하며,상기 나노 패턴은 제1 패턴부 및 제2 패턴부를 포함하며, 상기 제1 및 제2 패턴부는 서로 교번하여 배치되고,상기 기판과 상기 제1 패턴부는 동일한 물질을 포함하며,상기 기판과 상기 제1 패턴부는 백금(Pt), 구리(Cu), 은(Ag) 또는 금(Au) 중 하나 이상을 포함하고, 상기 제2 패턴부는 니켈(Ni), 코발트(Co) 또는 티타늄(Ti) 중 하나 이상을 포함하는,전도체. |

| 12 | 제11 항에 있어서,상기 2차원 물질층은 이황화 몰리브텐(MoS2) 또는 이황화 텅스텐(WS2) 중 하나 이상을 포함하는,전도체. |

| 13 | 기판의 상부에 나노 패턴의 형상을 구비하는 마스크 층을 증착시키는 단계;상기 마스크 층의 일부를 제거하는 단계; 상기 기판을 에칭하는 단계;상기 에칭된 기판의 상부에 금속층을 증착시키는 단계;상기 마스크 층의 나머지 부분을을 제거하는 단계; 및 상기 기판의 상부에 그래핀 층을 형성하는 단계;를 포함하며,상기 나노 패턴과 상기 금속층은 서로 교번하여 배치되고,상기 기판과 상기 나노 패턴은 동일한 물질을 포함하고,상기 기판과 상기 나노 패턴은 백금(Pt), 구리(Cu), 은(Ag) 또는 금(Au) 중 하나 이상을 포함하고, 상기 금속층은 니켈(Ni), 코발트(Co) 또는 티타늄(Ti) 중 하나 이상을 포함하는,전도체의 제조 방법. |

| 14 | 제 13 항에 있어서, 상기 마스크 층은 복수 개의 폴리머 블록을 구비하는 블록 코폴리머 필름인,전도체의 제조 방법. |

| 15 | 제 14 항에 있어서, 상기 복수 개의 폴리머 블록 중 어느 하나는 상기 나노 패턴의 형상을 따라 배치되는,전도체의 제조 방법. |

| 16 | 제 13 항에 있어서, 상기 나노 패턴은 일 방향으로 연장되는 선형 구조를 포함하며, 상기 선형 구조는 소정의 간격을 사이에 두고 서로 이격되도록 배치되는전도체의 제조 방법. |

| 17 | 제 13 항에 있어서, 상기 나노 패턴은 격자를 포함하며, 상기 격자는 상기 기판 상에 규칙적으로 배열되는,전도체의 제조 방법. |