| 번호 | 청구항 |

|---|---|

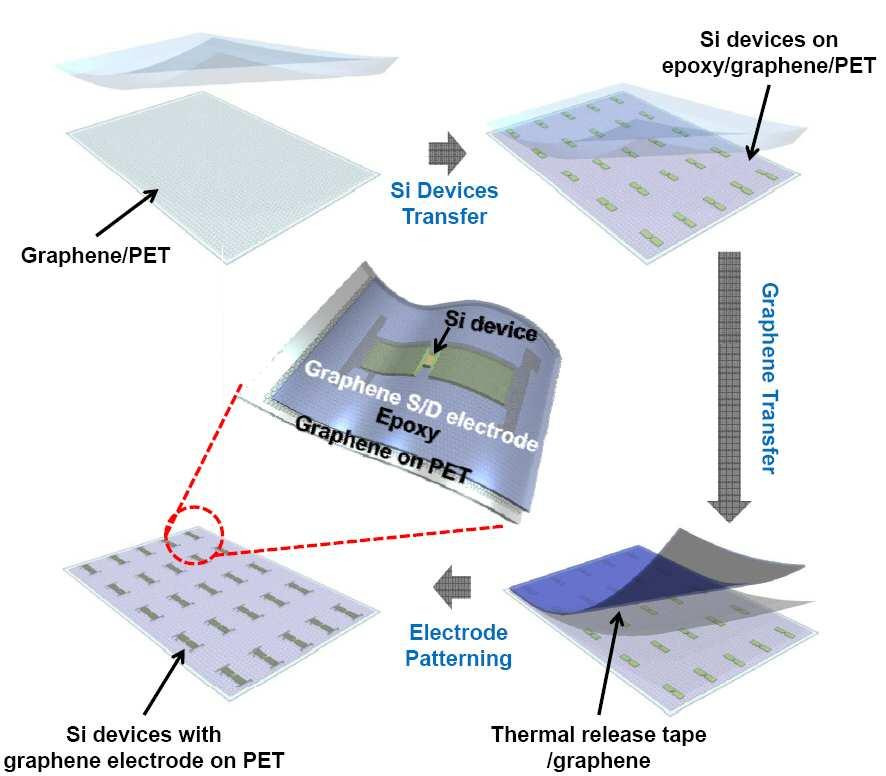

| 1 | 플렉시블(flexible)하고 스트레처블(stretchable)한 기판;상기 기판에 형성된 반도체층; 및,상기 반도체층에 형성된 스트레처블 그래핀 전극을 포함하는, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 그래핀 전극과 상기 반도체층 사이의 자연산화막을 제거함으로써 상기 그래핀 전극과 상기 반도체층 사이의 접촉저항을 감소시킨, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 그래핀 전극에 의하여 상기 그래핀 전극과 상기 반도체층 사이의 접촉저항을 감소시킨, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 그래핀 전극과 상기 반도체층 사이에 버퍼층을 형성하여 상기 그래핀 전극과 상기 반도체층 사이의 접촉저항을 감소시킨, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 그래핀 전극 상에 접촉저항 감소층을 형성하여 상기 그래핀 전극과 상기 반도체층 사이의 접촉저항을 감소시킨, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 그래핀 전극은 투명한 것인, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 1 항에 있어서,상기 반도체층은 유기물 반도체 또는 무기물 반도체를 포함하는 것인, 플렉시블/스트레처블 반도체 소자. |

| 1 | 제 7 항에 있어서,상기 무기물 반도체는 Si, 탄소나노튜브, 그래핀, 화합물 반도체, 산화물 반도체 및 이들의 조합들로 이루어진 군에서 선택되는 것인, 플렉시블/스트레처블 반도체 소자. |

| 1 | 반도체층과 그에 형성된 그래핀 전극 사이의 접촉저항을 감소시키는 방법으로서, (1) 상기 그래핀 전극과 상기 반도체층 사이의 자연산화막을 제거하는 것, (2) 상기 그래핀 전극과 상기 반도체층과의 접촉 면적을 가능한 넓게 되도록 형성하는 것, (3) 상기 그래핀 전극과 상기 반도체층 사이에 버퍼층을 형성하는 것, 및 (4) 상기 그래핀 전극 상에 접촉저항 감소층을 형성하는 것으로 이루어진 군에서 선택되는 하나 이상을 포함하는, 반도체층과 그래핀 전극 사이의 접촉저항을 감소시키는 방법. |

| 1 | 제 9 항에 있어서,상기 반도체층은 유기물 반도체 또는 무기물 반도체를 포함하는 것인, 반도체층과 그래핀 전극 사이의 접촉저항을 감소시키는 방법. |

| 1 | 제 9 항에 있어서,상기 (3) 및 (4)에서 상기 버퍼층 및 접촉저항 감소층 각각은 도전성 물질을 포함하여 형성되는 것인, 반도체층과 그래핀 전극 사이의 접촉저항을 감소시키는 방법. |

| 1 | 제 11 항에 있어서,상기 도전성 물질은 ITO, IZO, Ti, Cu, Au, Pt, Ir, Cr, Mg, Ag, Ni, Al 및 이들의 조합들로 이루어진 군에서 선택되는 것을 포함하는 것인, 반도체층과 그래핀 전극 사이의 접촉저항을 감소시키는 방법. |

| 1 | 탄성체 기판;상기 탄성체 기판 상에 형성되는 복수개의 소자; 및상기 복수개의 소자를 상호 연결하는 그래핀 인터커넥터를 포함하는, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 그래핀 인터커넥터는 도핑된 그래핀층으로 형성되는 것인, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 그래핀 인터커넥터는 복수개의 그래핀층을 적층하여 형성되는 것인, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 그래핀 인터커넥터는 그래핀층 및 상기 그래핀층에 증착된 금속 나노입자를 포함하는 것인, 전자 디바이스. |

| 1 | 제 16 항에 있어서,상기 금속 나노입자는 Ag, Au, Pt, Pd, Fe, Ni, Al, Sb, W, Tb, Dy, Gd, Eu, Nd, Pr, Sr, Mg, Cu, Zn, Co, Mn, Cr, V, Mo, Zr, Ba 및 이들의 조합들로 이루어진 군에서 선택되는 것을 포함하는 것인, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 그래핀 인터커넥터는 금속 나노입자 및 그래핀층을 교대로 복수회 적층하여 형성되는 것인, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 탄성체 기판은 열가소성 탄성 중합체(thermoplastic elastomer), 스티렌계 물질(styrenic materials), 올레핀계 물질(olefenic materials), 폴리올레핀(polyolefin), 폴리우레탄 열가소성 탄성 중합체(polyurethane thermoplastic elastomers), 폴리아미드(polyamides), 합성고무(synthetic rubbers), 폴리디메틸실록산(polydimethylsiloxane; PDMS), 폴리부타디엔(polybutadiene), 폴리이소부티렌(polyisobutylene), 폴리(스티렌-부타디엔-스티렌)(poly(styrene-butadiene-styrene)), 폴리우레탄(polyurethanes), 폴리클로로프렌(polychloroprene), 실리콘 및 이들의 조합들로 이루어진 군에서 선택되는 것인, 전자 디바이스. |

| 1 | 제 13 항에 있어서,상기 탄성체 기판은 1% 내지 30%의 변형률로 변형되는 것인, 전자 디바이스. |