| 번호 | 청구항 |

|---|---|

| 2 | 제1항에서,상기 칼코겐 함유 이차원 반도체 물질은 금속 칼코게나이드 나노플레이크를 포함하는 연신 박막 트랜지스터. |

| 3 | 제2항에서,상기 금속 칼코게나이드 나노플레이크는 Mo, W, Nb, Ta, Pt, Pd, Co, Cr, Cu, Ni 또는 이들의 조합에서 선택된 금속 원소와 S, Se, Te 또는 이들의 조합에서 선택된 칼코겐 원소를 포함하는 연신 박막 트랜지스터. |

| 4 | 제2항에서,상기 치환 또는 비치환된 아릴 칼코겐올의 칼코겐 원소는 상기 금속 칼코게나이드 나노플레이크에 고정되어 있는 연신 박막 트랜지스터. |

| 5 | 제2항에서,상기 금속 칼코게나이드 나노플레이크와 상기 치환 또는 비치환된 아릴 칼코겐올은 칼코겐 원소를 공유하여 화학 결합되어 있는 연신 박막 트랜지스터. |

| 6 | 제2항에서,상기 치환 또는 비치환된 아릴 칼코겐올 유도체는 상기 치환 또는 비치환된 아릴 칼코겐올로부터 유래된 치환 또는 비치환된 방향족 화합물을 포함하는 연신 박막 트랜지스터. |

| 1 | 게이트 전극,상기 게이트 전극과 중첩하게 위치하는 반도체 층,상기 게이트 전극과 상기 반도체 층 사이에 위치하는 게이트 절연층, 그리고 상기 반도체 층과 전기적으로 연결되어 있는 소스 전극과 드레인 전극을 포함하고,상기 반도체 층은 칼코겐 함유 이차원 반도체 물질 및 치환 또는 비치환된 아릴 칼코겐올 또는 그 유도체를 포함하는 연신 박막 트랜지스터. |

| 7 | 제2항에서,상기 반도체 층은 상기 금속 칼코게나이드 나노플레이크가 상기 반도체 층의 면내 방향을 따라 배열되어 있는 금속 칼코게나이드 나노플레이크 단층을 1개 또는 복수 개 포함하고,상기 치환 또는 비치환된 아릴 칼코겐올 또는 그 유도체는 상기 금속 칼코겐나이드 나노플레이크 단층의 표면에 위치하거나 인접한 상기 금속 칼코겐나이드 나노플레이크 단층 사이에 위치하는 연신 박막 트랜지스터. |

| 8 | 제1항에서,상기 치환 또는 비치환된 아릴 칼코겐올에 포함된 칼코겐 원소의 적어도 일부는 상기 칼코겐 함유 이차원 반도체 물질에 포함된 칼코겐 원소와 동일한 연신 박막 트랜지스터. |

| 9 | 제1항에서,상기 치환 또는 비치환된 아릴 칼코겐올은 하기 화학식 2A로 표현되는 연신 박막 트랜지스터:[화학식 2A]상기 화학식 2A에서,X는 S, Se 또는 Te이고,R1 내지 R5는 각각 독립적으로 수소, 중수소, 치환 또는 비치환된 C1 내지 C30 알킬기, 치환 또는 비치환된 C2 내지 C30 알케닐기, 치환 또는 비치환된 C6 내지 C30 아릴기, 치환 또는 비치환된 C3 내지 C30 헤테로고리기, 시아노기, 할로겐 또는 이들의 조합이다. |

| 10 | 제9항에서,R1 내지 R5 중 적어도 하나는 할로겐을 포함하는 연신 박막 트랜지스터. |

| 11 | 제1항에서,상기 치환 또는 비치환된 아릴 칼코겐올은 하나 이상의 할로겐으로 치환된 아릴 칼코겐올을 포함하는 연신 박막 트랜지스터. |

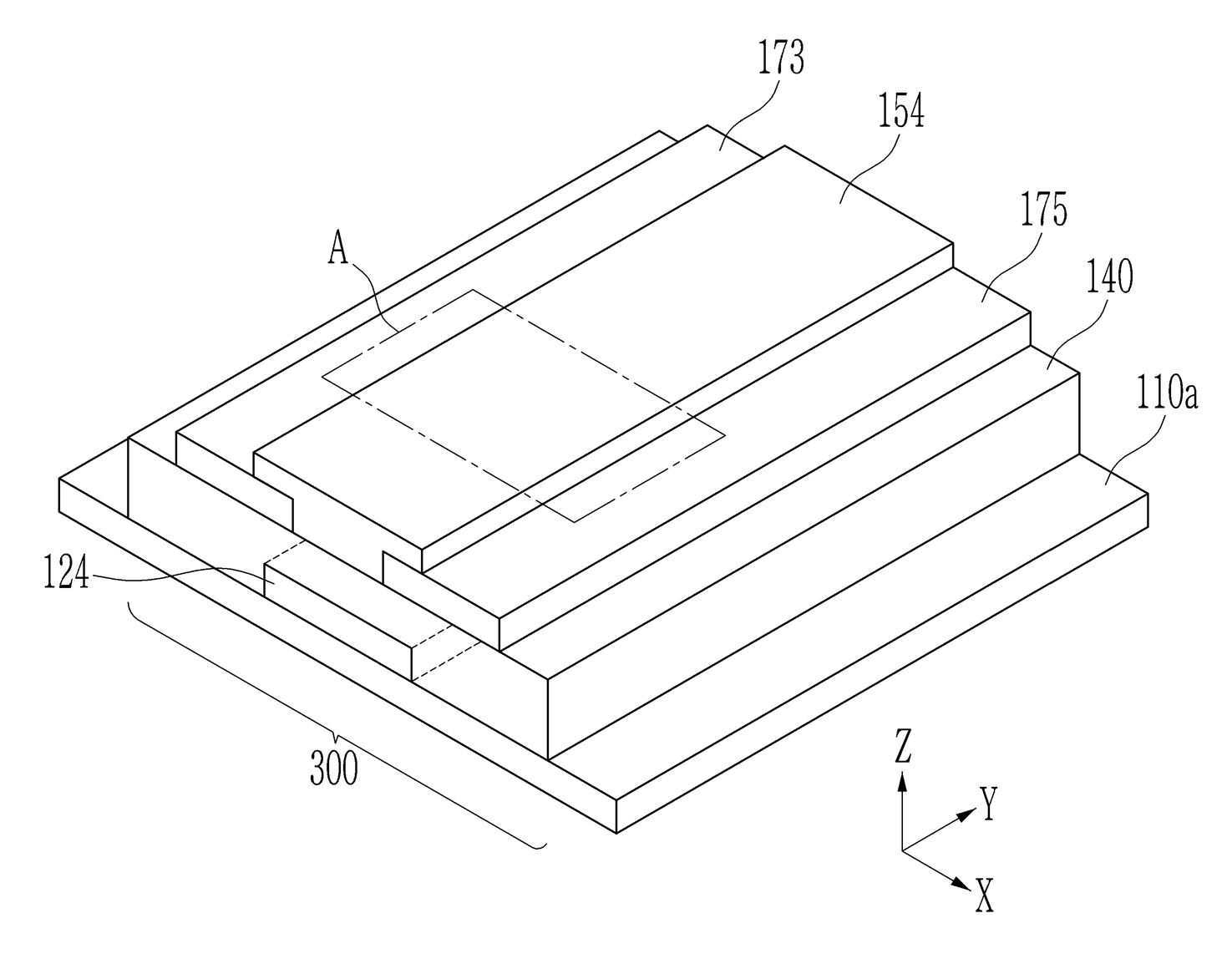

| 12 | 제1항에서,상기 게이트 전극, 상기 소스 전극 및 상기 드레인 전극은 각각 독립적으로 미세크랙 금속, 액체 금속, 도전성 나노구조체, 도전성 고분자 또는 이들의 조합을 포함하고,상기 게이트 절연층은 폴리오가노실록산, 부타디엔 구조단위를 포함하는 중합체, 올레핀 구조단위를 포함하는 중합체, 우레탄 구조단위를 포함하는 중합체, 아크릴 구조단위를 포함하는 중합체 또는 이들의 조합을 포함하는 연신 박막 트랜지스터. |

| 13 | 연신 기판,상기 연신 기판 위에 배열되어 있고 제1항 내지 제12항 중 어느 한 항에 따른 연신 박막 트랜지스터를 포함하는 연신 박막 트랜지스터 어레이, 그리고상기 각 연신 박막 트랜지스터에 전기적으로 연결되어 있는 단위 소자를 포함하는 단위 소자 어레이를 포함하는 연신 패널. |

| 14 | 제13항에서,상기 연신 기판의 일부와 중첩하게 형성되어 있고 상기 연신 기판보다 높은 탄성 모듈러스를 가지는 비연신 패턴을 더 포함하고,상기 연신 패널은상기 비연신 패턴이 형성되어 있는 고탄성 모듈러스 영역, 그리고상기 고탄성 모듈러스 영역을 제외한 저탄성 모듈러스 영역을 포함하는 연신 패널. |

| 15 | 제14항에서,상기 연신 기판은 폴리오가노실록산, 부타디엔 구조단위를 포함하는 중합체, 올레핀 구조단위를 포함하는 중합체, 우레탄 구조단위를 포함하는 중합체, 아크릴 구조단위를 포함하는 중합체 또는 이들의 조합을 포함하고,상기 비연신 패턴은 폴리카보네이트, 폴리메틸메타크릴레이트, 폴리에틸렌테레프탈레이트, 폴리에틸렌나프탈레이트, 폴리이미드, 폴리아미드, 폴리아미드이미드, 폴리에테르술폰 또는 이들의 조합을 포함하는 연신 패널. |

| 16 | 제14항에서,상기 연신 박막 트랜지스터는 상기 고탄성 모듈러스 영역에 위치하는 연신 패널. |

| 17 | 제14항에서,상기 연신 박막 트랜지스터는 상기 저탄성 모듈러스 영역에 위치하는 연신 패널. |

| 18 | 제14항에서,상기 단위 소자는 발광 다이오드, 광전변환다이오드 또는 이들의 조합을 포함하고,상기 단위 소자는 상기 고탄성 모듈러스 영역에 위치하는 연신 패널. |

| 19 | 제13항에서,상기 연신 패널은 연신 디스플레이 또는 연신 센서 어레이인 연신 패널. |

| 20 | 제13항 내지 제19항 중 어느 한 항에 따른 연신 패널을 포함하는 전자 장치. |