| 번호 | 청구항 |

|---|---|

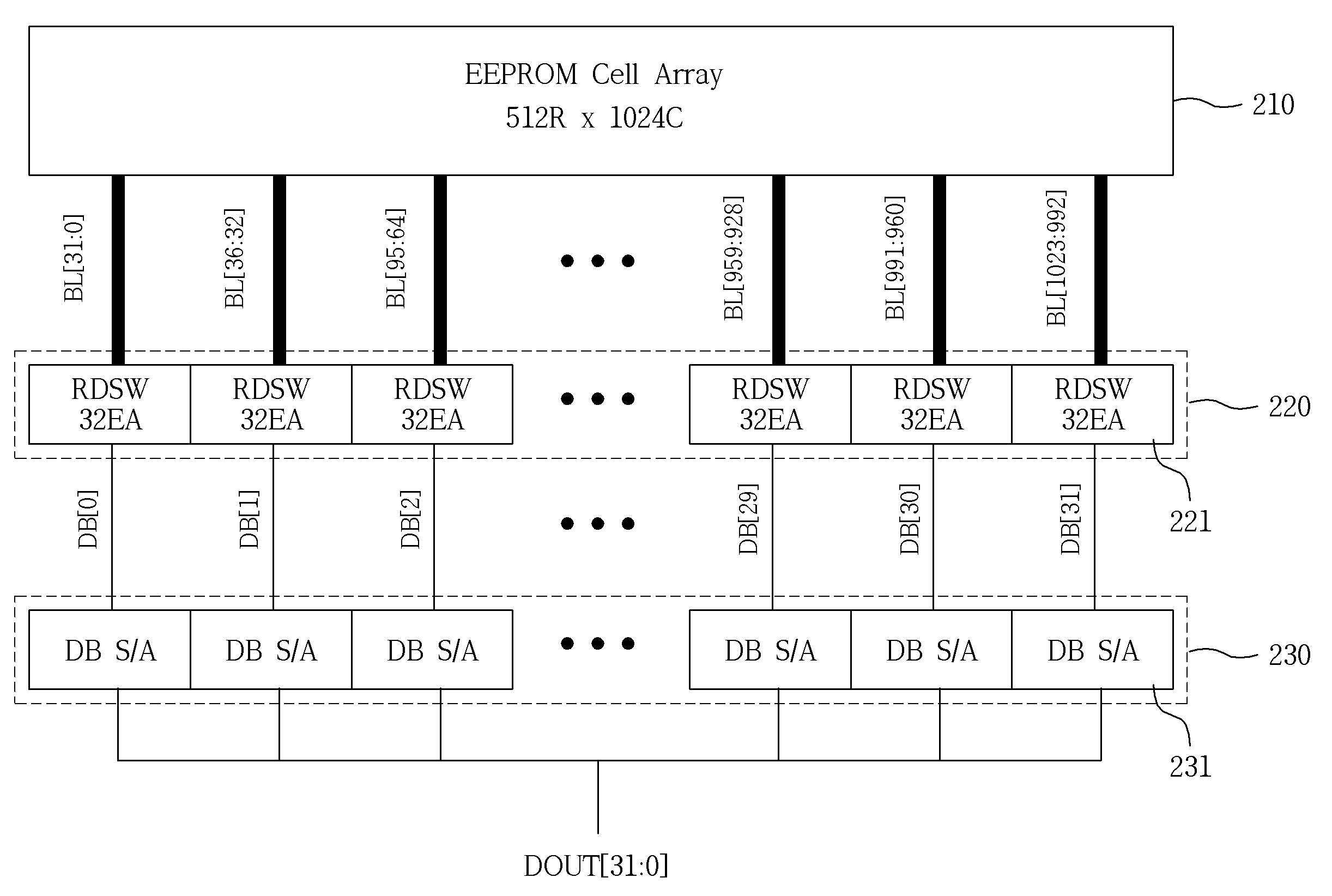

| 1 | 이이피롬 셀 어레이:상기 이이피롬 셀 어레이에 대하여 32 개로 분할된 비트라인 스위치회로부를 구비하고, 상기 비트라인 스위치회로부들은 각각 32개의 비트라인 스위치회로를 구비하여 비트라인과 데이터라인 간의 선택적 연결을 위한 스위칭 동작을 수행하는 비트라인 제어부; 및 상기 이이피롬 셀 어레이에 대하여 32개로 분할된 데이터라인 센스앰프를 구비하는 로컬 데이터라인 센싱 구조를 갖는 데이터라인 센스 앰프부;를 포함하되,상기 비트라인 스위치 회로는,펌프인에이블신호에 따라 비트라인스위치 디스에이블반전신호를 출력하는 디스에이블반전신호 출력부;상기 비트라인스위치 디스에이블반전신호에 의해 턴온되어 상기 비트라인을 제1노드에 연결하는 비트라인 연결 제어부;제1,2리드제어신호에 따라 비트라인스위치 선택신호를 출력하는 선택신호 출력부; 및상기 비트라인스위치 선택신호에 의해 상기 제1노드를 상기 데이터라인에 연결하고, 비트라인스위치 클램프신호에 따라 상기 제1노드의 신호를 클램프하는 선택 및 클램핑부를 포함하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 2 | 삭제 |

| 3 | 제1항에 있어서, 상기 디스에이블반전신호 출력부는듀얼 프로그램 전압을 이용하여 상기 이이피롬 셀 어레이의 셀에 대한 지우기와 프로그램 동작을 수행하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 4 | 제3항에 있어서, 상기 듀얼 프로그램 전압은 ±7.25V인 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 5 | 제1항에 있어서, 상기 디스에이블반전신호 출력부는 펌프인에이블신호를 3단 차동증폭하는 제1-3증폭부; 및상기 제3증폭부의 출력신호를 반전시켜 상기 비트라인스위치 디스에이블반전신호로 출력하는 반전증폭부를 포함하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 6 | 제1항에 있어서, 상기 선택신호 출력부는 외부로부터 공급되는 제1,2리드제어신호를 낸드 연산하는 낸드게이트; 타측 단자와 게이트가 서로 교차 결합된 제21,22 피모스 트랜지스터, 차동결합된 제21,22 엔모스 트랜지스터 및 상기 낸드게이트의 출력단과 상기 제22엔모스 트랜지스터의 게이트 사이에 연결된 제21인버터를 구비하여, 상기 낸드게이트의 출력신호를 차동 증폭하는 차동 증폭단; 및 전원전압과 접지전압의 사이에 직렬 연결된 제23피모스 트랜지스터 및 제23엔모스 트랜지스터를 구비하여, 상기 차동증폭단의 출력신호를 반전시켜 상기 비트라인스위치 선택신호로 출력하는 반전 증폭단을 포함하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 7 | 제1항에 있어서, 상기 데이터라인 센스앰프는상기 데이터라인의 전압을 클램핑하는 데이터라인 클램핑회로; 읽기 모드에서 상기 데이터라인을 로우전원전압으로 풀업시키는 데이터라인 풀업부;상기 데이터라인의 전압과 기준전압의 차전압을 증폭하는 차동센스 앰프; 및 상기 차동센스 앰프의 출력신호를 래치하여 그에 따른 데이터를 데이터출력단자에 출력하는 래치부를 포함하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |

| 8 | 제7항에 있어서, 상기 데이터라인 클램핑회로는상기 데이터라인의 전압과 데이터라인 클램프반전신호를 노아 연산하는 제60노아게이트; 및상기 제60노아게이트의 출력신호에 따라 상기 데이터라인의 전압을 소정의 레벨로 클램핑하는 제60엔모스 트랜지스터를 포함하는 것을 특징으로 하는 이이피롬의 데이터버스 회로. |