| 번호 | 청구항 |

|---|---|

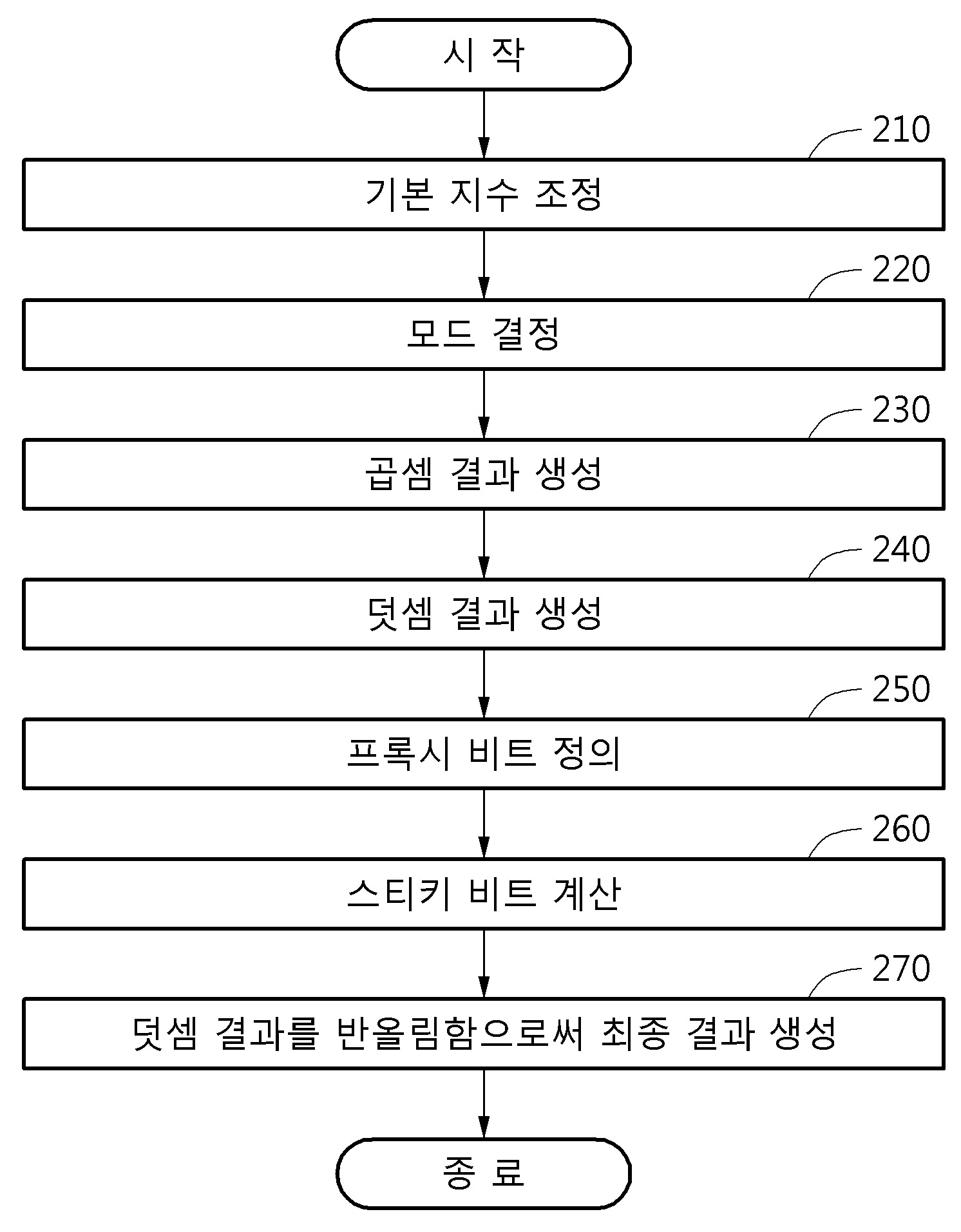

| 1 | 가중된 두 단계 부스 알고리즘(weighted two-level booth algorithm)을 이용하여 제1 부동 소수점의 지수 및 제2 부동 소수점의 지수가 서로 대응하도록, 상기 제1 부동 소수점 및 상기 제2 부동 소수점 중 적어도 하나의 기본 지수를 조정하는 단계;상기 제1 부동 소수점의 기본 지수, 상기 제2 부동 소수점의 기본 지수 및 제3 부동 소수점의 기본 지수에 기반하여, 미리 설정된 복수의 모드들 중 상기 제1 부동 소수점의 가수 및 상기 제2 부동 소수점의 가수를 곱한 곱셈 결과에 상기 제3 부동 소수점의 가수를 더하는 모드를 결정하는 단계;상기 곱셈 결과를 생성하는 단계;상기 곱셈 결과에 상기 제3 부동 소수점의 가수를 더함으로써 덧셈 결과를 생성하는 단계;상기 결정된 모드에 기반하여 상기 덧셈 결과 내에 두 개의 프록시(proxy) 비트들을 정의하는 단계;상기 두 개의 프록시 비트들에 기반하여 두 개의 스티키(sticky) 비트들을 각각 계산하는 단계; 및상기 스티키 비트들에 기반하여 상기 덧셈 결과를 반올림함으로써 최종 결과를 생성하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 2 | 제1항에 있어서,상기 미리 설정된 복수의 모드들 중 상기 모드를 결정하는 단계는,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 3 | 제2항에 있어서,상기 미리 설정된 복수의 모드들은 4개의 모드들인,단일 곱셈-누산 방법. |

| 4 | 제2항에 있어서,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는 단계는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 56이상인 경우 제1 모드로 결정하는 단계를 포함하고,상기 덧셈 결과를 생성하는 단계는,상기 모드가 제1 모드로 결정된 경우, 상기 제3 부동 소수점의 가수의 53 비트들을 상기 덧셈 결과의 상위 53 비트들로 생성하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 5 | 제2항에 있어서,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는 단계는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 0 이상이고, 56미만인 경우 제2 모드로 결정하는 단계를 포함하고,상기 덧셈 결과를 생성하는 단계는,상기 모드가 제2 모드로 결정된 경우, 상기 곱셈 결과 및 제3 부동 소수점의 가수를 더한 결과 중 상위 53 비트들을 상기 덧셈 결과의 상위 53 비트들로 생성하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 6 | 제2항에 있어서,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는 단계는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 -57을 초과하고, 0 이하인 경우 제3 모드로 결정하는 단계를 포함하고,상기 덧셈 결과를 생성하는 단계는,상기 모드가 제3 모드로 결정된 경우, 상기 곱셈 결과에 상기 제3 부동 소수점의 가수를 더함으로써 상기 덧셈 결과를 생성하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 7 | 제2항에 있어서,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는 단계는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 -57이하인 경우 제4 모드로 결정하는 단계를 포함하고,상기 덧셈 결과를 생성하는 단계는,상기 모드가 제4 모드로 결정된 경우, 상기 곱셈 결과의 상위 54 비트들을 상기 덧셈 결과의 상위 54 비트들로 생성하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 8 | 제1항에 있어서,상기 두 개의 프록시 비트들을 정의하는 단계는,상기 덧셈 결과의 라운드 비트의 오른쪽 첫 번째 비트 및 오른쪽 두 번째 비트를 상기 두 개의 프록시 비트들로 정의하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 9 | 제1항에 있어서,상기 두 개의 스티키 비트들을 각각 계산하는 단계는,상기 두 개의 프록시 비트들을 논리 오어 연산(logical OR operation)함으로써 제1 스티키 비트를 계산하는 단계; 및상기 곱셈 결과와 상기 제3 부동 소수점의 가수를 더한 결과 중 상기 덧셈 결과에 영향을 미치지 않는 비트들에 기반하여 제2 스티키 비트를 계산하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 10 | 제1항에 있어서,상기 가중된 두 단계 부스 알고리즘을 이용하여 상기 제1 부동 소수점, 상기 제2 부동 소수점 및 상기 제3 부동 소수점 중 적어도 하나의 기본 지수를 조정하는 단계는,기본 지수에 적용된 제1 부스 인코딩 단위보다 더 낮은 제2 부스 인코딩 단위를 이용하여 상기 제1 부동 소수점, 상기 제2 부동 소수점 및 상기 제3 부동 소수점 중 적어도 하나의 기본 지수를 조정하는 단계를 포함하는,단일 곱셈-누산 방법. |

| 11 | 가중된 두 단계 부스 알고리즘(weighted two-level booth algorithm)을 이용하여 제1 부동 소수점의 지수 및 제2 부동 소수점의 지수가 서로 대응하도록, 상기 제1 부동 소수점 및 상기 제2 부동 소수점 중 적어도 하나의 기본 지수를 조정하고,상기 제1 부동 소수점의 기본 지수, 상기 제2 부동 소수점의 기본 지수 및 제3 부동 소수점의 기본 지수에 기반하여, 미리 설정된 복수의 모드들 중 상기 제1 부동 소수점의 가수 및 상기 제2 부동 소수점의 가수를 곱한 곱셈 결과에 상기 제3 부동 소수점의 가수를 더하는 모드를 결정하고,상기 곱셈 결과를 생성하고,상기 곱셈 결과에 상기 제3 부동 소수점의 가수를 더함으로써 덧셈 결과를 생성하고,상기 결정된 모드에 기반하여 상기 덧셈 결과 내에 두 개의 프록시(proxy) 비트들을 정의하고,상기 두 개의 프록시 비트들에 기반하여 두 개의 스티키(sticky) 비트들을 각각 계산하고,상기 스티키 비트들에 기반하여 상기 덧셈 결과를 반올림함으로써 최종 결과를 생성하는, 처리부; 및상기 제1 부동 소수점, 상기 제2 부동 소수점 및 상기 제3 부동 소수점을 저장하는 메모리를 포함하는,단일 곱셈-누산 장치. |

| 12 | 제11항에 있어서,상기 처리부는,상기 제3 부동 소수점의 기본 지수에서 상기 제1 부동 소수점의 기본 지수 및 상기 제2 부동 소수점의 기본 지수를 곱한 값을 뺀 값에 기반하여 상기 모드를 결정하는,단일 곱셈-누산 장치. |

| 13 | 제12항에 있어서,상기 미리 설정된 복수의 모드들은 4개의 모드들인,단일 곱셈-누산 장치. |

| 14 | 제12항에 있어서,상기 처리부는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 56이상인 경우 제1 모드로 결정하고,상기 모드가 제1 모드로 결정된 경우, 상기 제3 부동 소수점의 가수의 53 비트들을 상기 덧셈 결과의 상위 53 비트들로 생성하는,단일 곱셈-누산 장치. |

| 15 | 제12항에 있어서,상기 처리부는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 0 이상이고, 56미만인 경우 제2 모드로 결정하고,상기 모드가 제2 모드로 결정된 경우, 상기 곱셈 결과 및 제3 부동 소수점의 가수를 더한 결과 중 상위 53 비트들을 상기 덧셈 결과의 상위 53 비트들로 생성하는,단일 곱셈-누산 장치. |

| 16 | 제12항에 있어서,상기 처리부는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 -57을 초과하고, 0 이하인 경우 제3 모드로 결정하고,상기 모드가 제3 모드로 결정된 경우, 상기 곱셈 결과에 상기 제3 부동 소수점의 가수를 더함으로써 상기 덧셈 결과를 생성하는,단일 곱셈-누산 장치. |

| 17 | 제12항에 있어서,상기 처리부는,상기 부동 소수점들이 64 비트들로 각각 표현되고, 상기 뺀 값이 -57이하인 경우 제4 모드로 결정하고,상기 모드가 제4 모드로 결정된 경우, 상기 곱셈 결과의 상위 54 비트들을 상기 덧셈 결과의 상위 54 비트들로 생성하는,단일 곱셈-누산 장치. |

| 18 | 제11항에 있어서,상기 처리부는,상기 덧셈 결과의 라운드 비트의 오른쪽 첫 번째 비트 및 오른쪽 두 번째 비트를 상기 두 개의 프록시 비트들로 정의하는,단일 곱셈-누산 장치. |

| 19 | 제11항에 있어서,상기 처리부는,상기 두 개의 프록시 비트들을 논리 오어 연산(logical OR operation)함으로써 제1 스티키 비트를 계산하고, 상기 곱셈 결과와 상기 제3 부동 소수점의 가수를 더한 결과 중 상기 덧셈 결과에 영향을 미치지 않는 비트들에 기반하여 제2 스티키 비트를 계산하는,단일 곱셈-누산 장치. |

| 20 | 제11항에 있어서,상기 처리부는,기본 지수에 적용된 제1 부스 인코딩 단위보다 더 낮은 제2 부스 인코딩 단위를 이용하여 상기 제1 부동 소수점, 상기 제2 부동 소수점 및 상기 제3 부동 소수점 중 적어도 하나의 기본 지수를 조정하는,단일 곱셈-누산 장치. |