| 번호 | 청구항 |

|---|---|

| 2 | 제1항에 있어서,상기 산화물 반도체층의 두께가 10 nm 미만인 박막 트랜지스터. |

| 3 | 제1항에 있어서,상기 게이트 절연막의 두께가 5 nm 내지 200 nm 범위 내인 박막 트랜지스터. |

| 4 | 제1항에 있어서,상기 게이트 절연막이 포함하는 유전상수가 7 이상인 물질이 산화지르코늄, 산화알루미늄, 산화티타늄, 산화하프늄 및 산화탄탈 중 적어도 하나를 포함하는 박막 트랜지스터. |

| 5 | 삭제 |

| 6 | 제1항에 있어서,1.0 V의 Vgs 및 0.1 V의 Vds에서의 선형 영역 전계 효과 이동도가 7 cm2V-1s-1 이상인 박막 트랜지스터. |

| 7 | 제1항에 있어서,1.0 V 이하의 Vgs-Von에서 활성화 에너지가 40 meV 이하인 박막 트랜지스터. |

| 8 | 제1항에 있어서,40 meV 이하의 전도대 아래 에너지 레벨에서 상태밀도가 1020 states/(eV*cm3) 이상인 박막 트랜지스터. |

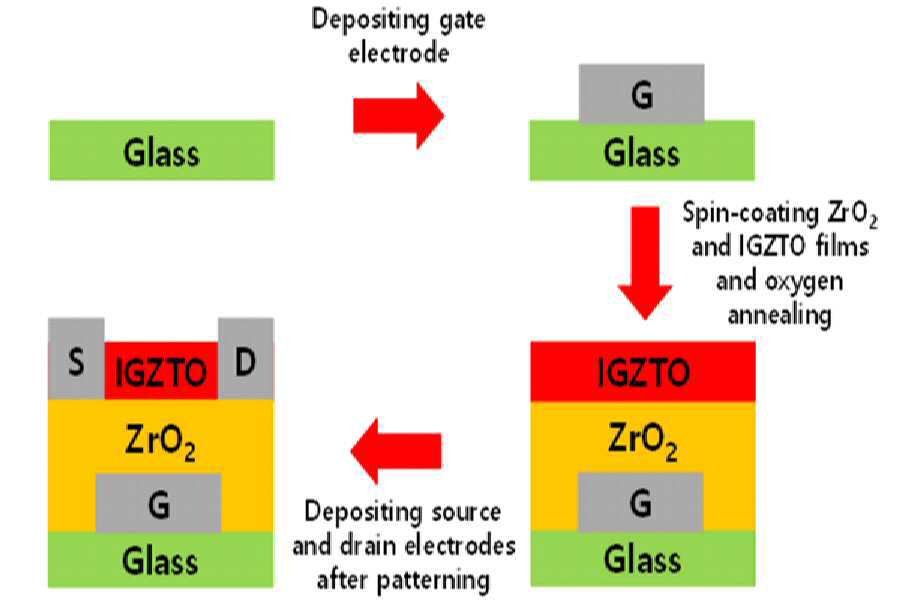

| 1 | 게이트 전극, 게이트 절연막 및 산화물 반도체층을 이 순서로 포함하고,상기 게이트 절연막이 유전상수가 7 이상인 물질을 포함하고,상기 산화물 반도체층이 IGZTO를 포함하고,상기 산화물 반도체층의 M-O 비율이 70 % 이상이며, 네거티브 바이어스 일루미네이션 스트레스 인가 전후의 문턱 전압 차이가 0.15 V 이하이고, 포지티브 바이어스 일루미네이션 스트레스 인가 전후의 문턱 전압 차이가 0.15 V 이하인 박막 트랜지스터. |

| 9 | 유전상수가 7 이상인 물질의 전구체를 포함하는 게이트 절연막 형성용 용액으로 게이트 전극 상에 게이트 절연막을 형성하는 단계; 및인듐 전구체, 갈륨 전구체, 아연 전구체, 및 주석 전구체를 포함하는 산화물 반도체층 형성용 용액으로 상기 게이트 절연막 상에 산화물 반도체층을 형성하는 단계;를 포함하고,상기 게이트 절연막을 형성하는 단계 및 상기 산화물 반도체층을 형성하는 단계 각각이 90 부피% 이상의 산소 분위기 하에서의 열처리를 포함하며,네거티브 바이어스 일루미네이션 스트레스 인가 전후의 문턱 전압 차이가 0.15 V 이하이고, 포지티브 바이어스 일루미네이션 스트레스 인가 전후의 문턱 전압 차이가 0.15 V 이하인 박막 트랜지스터의 제조 방법. |

| 10 | 제9항에 있어서,상기 게이트 절연막 형성용 용액에서 유전상수가 7 이상인 물질의 전구체의 농도가 0.1 M 내지 1 M 범위 내인 박막 트랜지스터의 제조 방법. |

| 11 | 제9항에 있어서,상기 산화물 반도체층 형성용 용액에서 인듐 전구체, 갈륨 전구체, 아연 전구체, 및 주석 전구체 총합의 농도가 0.05 M 내지 0.5 M 범위 내인 박막 트랜지스터의 제조 방법. |

| 12 | 제9항에 있어서,상기 산화물 반도체층 형성용 용액에서 주석과 아연의 총 몰수에 대한 주석의 몰 수의 비율(Sn/(Sn+Zn))이 0.05 내지 0.5 범위 내인 박막 트랜지스터의 제조 방법. |

| 13 | 제9항에 있어서,상기 게이트 절연막을 형성하는 단계는 200 ℃ 내지 450 ℃ 범위 내 온도 하에서의 열처리를 포함하는 박막 트랜지스터의 제조 방법. |

| 14 | 제9항에 있어서,상기 산화물 반도체층을 형성하는 단계는 200 ℃ 내지 450 ℃ 범위 내 온도하에서의 열처리를 포함하는 박막 트랜지스터의 제조 방법. |

| 15 | 제1항의 박막 트랜지스터를 포함하는 전자 장치. |