| 번호 | 청구항 |

|---|---|

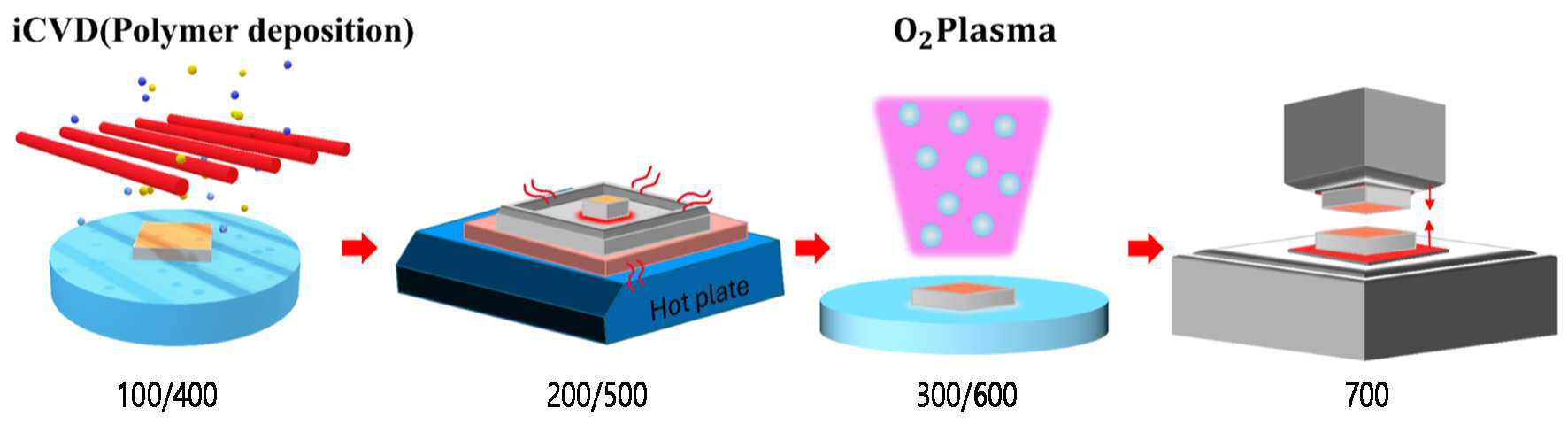

| 1 | 제1 반도체 구조체 상에 화학기상증착으로 제1 폴리머막을 증착하는 단계;상기 제1 폴리머막을 경화하는 단계; 경화된 제1 폴리머막의 표면에 플라즈마 처리하는 단계; 제2 반도체 구조체 상에 화학기상증착으로 제2 폴리머막을 형성하는 단계;상기 제2 폴리머막을 경화하는 단계; 경화된 제2 폴리머막의 표면에 플라즈마 처리하는 단계; 및 상기 제1 폴리머막 상에 상기 제2 폴리머막이 접촉하도록 제1 반도체 구조체 및 제2 반도체 구조체를 배치하고 접합하는 단계;를 포함하고, 상기 화학기상증착은 개시제를 이용하는 iCVD(initiated Chemical Vapor Deposition)인 것인, 반도체 적층 방법. |

| 2 | 제1항에 있어서,상기 제1 폴리머막 및 상기 제2 폴리머막은 각각, 폴리머 유전체를 포함하고, 상기 폴리머 유전체는 유전상수(k)가 3 이하이고,상기 제1 폴리머막 및 상기 제2 폴리머막은 각각, 1 nm(나노미터) 이하의 표면 거칠기를 갖는 것인, 반도체 적층 방법. |

| 3 | 제1항에 있어서,상기 제1 폴리머막을 증착하는 단계에서 상기 화학기상증착은 iCVD(Initiated chemical vapor deposition)를 이용하여 100 ℃ 이하의 기판 온도에서 제1 폴리머막을 증착하고,상기 화학기상증착은 개시제 및 모노머를 동시에 주입하여 제1 폴리머막을 증착하고,상기 제1 폴리머막을 경화하는 단계는, 증착된 상기 제1 폴리머막을 50 ℃ 내지 250 ℃ 온도에서 열처리하여 경화하는 것인, 반도체 적층 방법. |

| 4 | 제1항에 있어서,상기 제1 반도체 구조체 및 상기 제2 반도체 구조체는 각각, 1 ㎛(마이크로미터) 이하의 피치로 배열된 금속 패턴을 갖는 반도체 구조체이며,상기 플라즈마 처리는 O2, NH3, CF4, Ar, N2, 및 H2 중 적어도 하나 이상의 가스를 이용하고,상기 접합하는 단계는 0.1 Mpa내지 10 Mpa압력을 가하고,상기 접합하는 단계에서 형성된 상기 제1 폴리머막 및 상기 제2 폴리머막 간의 접합 영역은 8 Mpa 이상의 접합 세기를 갖고,상기 접합 영역에서 상기 제1 폴리머막 및 상기 제2 폴리머막은 각각, 80 % 이상(각 폴리머막 일면의 전체 면적 기준)의 접합 면적을 갖는 것인, 반도체 적층 방법. |

| 5 | 제1항 내지 제4항 중 어느 한 항의 방법으로 제조되고, 상기 방법을 m회 이상 (m은 1 이상의 정수이다.) 반복하여 제조되고, n개(n은 2 이상의 정수이다.)의 반도체 구조체가 제1 폴리머 및 제2 폴리머 간의 결합을 이용하여 수직 방향으로 적층된 것인, 3차원 다중-칩 반도체 소자. |