| 번호 | 청구항 |

|---|---|

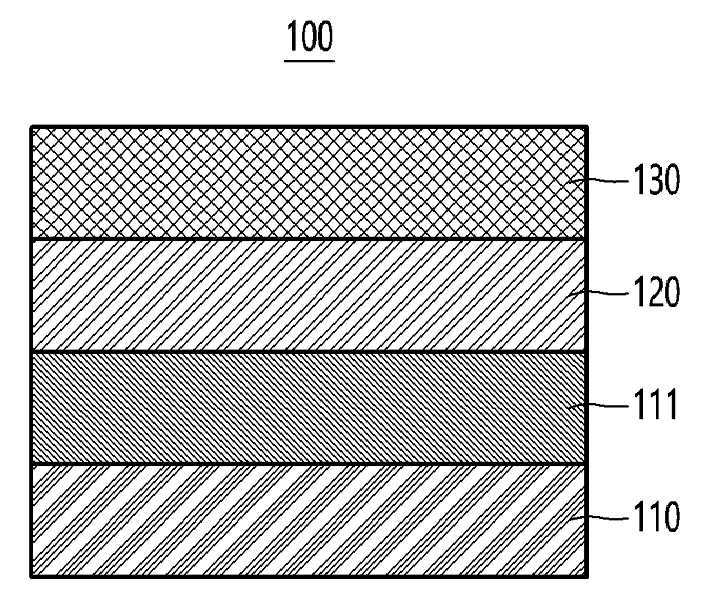

| 1 | 제1 전극층 및 제2 전극층을 포함하는 하부전극;상기 하부전극 상에 형성되는 유전체층; 및상기 유전체층 상에 형성되는 상부전극을 포함하고,상기 하부전극은 상기 제1 전극층과 상기 제2 전극층에서 농도 구배를 가지고, 상기 제2 전극층과 상기 제1 전극층의 두께 비율이 5:1 내지 1:5로 형성되는 것을 특징으로 하는반도체 소자용 커패시터. |

| 2 | 제1항에 있어서,상기 제1 전극층은 몰리브데넘 질화물(MoN)로 이루어지고,상기 제2 전극층은 티타늄 질화물(TiN)로 이루어지며,상기 유전체층은 Hf0.3Zr0.7O2 (HZO)로 이루어지고,상기 상부전극은 도핑된 폴리 실리콘, Al, Cu, Ti, Ta, Ru, W, Mo, Pt, Ni, Co, TiN, TaN, WN, NbN, TiAl, TiAlN, TiSi, TiSiN, TaSi, TaSiN, RuTiN, NiSi, CoSi, IrOx, RuOx, 또는 이들의 조합으로 이루어지는 것을 특징으로 하는반도체 소자용 커패시터. |

| 3 | 제2항에 있어서,상기 하부전극은 몰리브데넘 질화물 원자층 증착법과 티타늄 질화물 원자층 증착법을 조합한 슈퍼 사이클(super cycle)을 적용하여 상기 유전체층과의 계면은 티타늄의 농도가 많은 질화물을 기판과의 계면은 몰리브데넘의 농도가 많은 질화물로 농도 구배를 가지고,상기 슈퍼 사이클은 상기 몰리브데넘 질화물 원자층 증착법에 따라 몰리브데넘 전구체를 주입하고, 상기 몰리브데넘 전구체를 퍼지하고, NH3 플라즈마를 주입한 후 퍼지하는 m 사이클과 상기 티타늄 질화물 원자층 증착법에 따라 티타늄 전구체를 주입하고, 상기 티타늄 전구체를 퍼지하고, NH3 플라즈마를 주입한 후 퍼지하는 n 사이클을 포함하는 것을 특징으로 하는반도체 소자용 커패시터. |

| 4 | 제2항에 있어서,상기 하부전극은 상기 제1 전극층과 상기 제2 전극층의 전체 두께를 미리 설정된 두께로 형성되고, 상기 전체 두께에서 상기 제2 전극층의 두께 변화에 따라 산소 공공을 포함하고 있는 HfO2-x 상의 비율을 감소시켜 산소 소기 효과(scavenging effect)를 억제하여 누설 전류 특성을 개선하고, 상기 제2 전극층이 후속 열처리 과정에서 산소의 확산을 방지하여 후속 열처리 이후에도 0.8 nm 이하의 표면 거칠기를 갖도록 하여 산화 저항성을 증가시키며, 상기 제2 전극층에 기반하여 상기 제1 전극층의 일함수가 작용하여 일함수를 증가시키는 것을 특징으로 하는반도체 소자용 커패시터. |

| 5 | 제1 전극층 및 제2 전극층을 포함하는 하부전극을 형성하는 단계;상기 하부전극 상에 형성되는 유전체층을 형성하는 단계; 및상기 유전체층 상에 형성되는 상부전극을 형성하는 단계를 포함하고,상기 하부전극은 상기 제1 전극층과 상기 제2 전극층에서 농도 구배를 가지고, 상기 제2 전극층과 상기 제1 전극층의 두께 비율이 5:1 내지 1:5로 형성되며,상기 제1 전극층은 몰리브데넘 질화물(MoN)로 이루어지고,상기 제2 전극층은 티타늄 질화물(TiN)로 이루어지는 것을 특징으로 하는반도체 소자용 커패시터의 제조 방법. |