| 번호 | 청구항 |

|---|---|

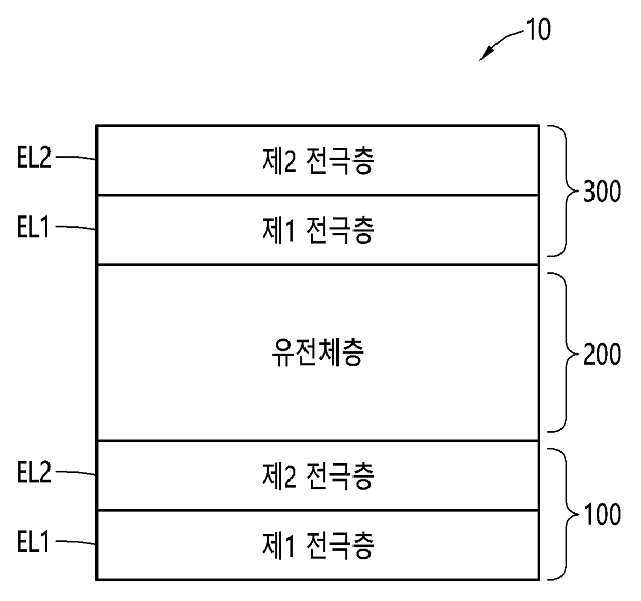

| 1 | 제1 전극층 및 제2 전극층을 포함하는 하부전극;상기 하부전극 상에 형성되는 유전체층; 및상기 유전체층 상에 형성되는 상부전극을 포함하고,상기 하부전극은 금속 또는 금속산화물(AOx (단, 0≤x003c#2))을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층으로 구성된 이중전극을 포함하고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리되고, 상기 제1 전극층 및 상기 제2 전극층 사이에 산화환원반응을 통하여 형성되되,상기 금속산화물은 루테늄산화물이고,상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리됨에 따라, 상기 제1 전극층에 증착된 루테늄산화물(RuOy (단, 0003c#y≤2))이 환원되고, 상기 제2 전극층에 증착된 몰리브데늄산화물(MoOz (단, 0≤z003c#2))이 산화됨으로써, 루테늄 또는 루테늄산화물(RuOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 구조를 가지는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 2 | 삭제 |

| 3 | 제1항에 있어서,상기 하부전극은 티타늄질화물(TiN)을 포함하는 베이스 전극층을 더 포함하고,상기 제1 전극층은 상기 베이스 전극층 상에 형성되는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 4 | 제1항에 있어서,상기 유전체층은 이산화티타늄(TiO2), Al, Hf, Zr, Ta 중 적어도 하나로 도핑된 이산화티타늄(Doped-TiO2), 이산화하프늄(HfO2), 이산화지르코늄(ZrO2), 오산화탄탈럼(Ta2O5), 및 산화알루미늄(Al2O3) 중 적어도 하나로 구성되고,상기 유전체층은 루타일 구조의 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층 상에 형성됨으로써, 유전율이 개선되는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 5 | 제1항에 있어서,상기 상부전극은,루테늄산화물(RuOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 상기 이중전극을 포함하는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 6 | 제1 전극층 및 제2 전극층을 포함하는 하부전극;상기 하부전극 상에 형성되는 유전체층; 및상기 유전체층 상에 형성되는 상부전극을 포함하고,상기 하부전극은 금속 또는 금속산화물(AOx (단, 0≤x003c#2))을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층으로 구성된 이중전극을 포함하고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리되고, 상기 제1 전극층 및 상기 제2 전극층 사이에 산화환원반응을 통하여 형성되되,상기 금속산화물은 이리듐산화물이고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리됨에 따라, 상기 제1 전극층에 증착된 이리듐산화물(IrOy (단, 0003c#y≤2))이 환원되고, 상기 제2 전극층에 증착된 몰리브데늄산화물(MoOz (단, 0≤z003c#2))이 산화됨으로써, 이리듐 또는 이리듐산화물(IrOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 구조를 가지는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 7 | 제1 전극층 및 제2 전극층을 포함하는 하부전극;상기 하부전극 상에 형성되는 유전체층; 및상기 유전체층 상에 형성되는 상부전극을 포함하고,상기 하부전극은 금속 또는 금속산화물(AOx (단, 0≤x003c#2))을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층으로 구성된 이중전극을 포함하고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리되고, 상기 제1 전극층 및 상기 제2 전극층 사이에 산화환원반응을 통하여 형성되되,상기 금속산화물은 레늄산화물이고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리됨에 따라, 상기 제1 전극층에 증착된 레늄산화물(ReOy (단, 0003c#y≤2))이 환원되고, 상기 제2 전극층에 증착된 몰리브데늄산화물(MoOz (단, 0≤z003c#2))이 산화됨으로써, 레늄 또는 레늄산화물(ReOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 구조를 가지는 것을 특징으로 하는,반도체 소자용 커패시터. |

| 8 | 하부전극을 형성하는 단계;상기 하부전극 상에 유전체층을 형성하는 단계; 및상기 유전체층 상에 상부전극을 형성하는 단계를 포함하고,상기 하부전극을 형성하는 단계는,제1 금속산화물(AOy (단, 0003c#y≤2))을 포함하는 제1 전극층을 증착하는 단계;몰리브데늄산화물(MoOz (단, 0≤z003c#2))을 포함하는 제2 전극층을 증착하는 단계;상기 제1 전극층 및 상기 제2 전극층을 열처리하는 단계; 및상기 제1 전극층 및 상기 제2 전극층 사이의 산화환원반응에 따라, 제2 금속 또는 제2 금속산화물(AOx (단, 0≤x003c#2))을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층으로 구성된 이중전극을 형성하는 단계를 포함하고,상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리됨에 따라, 상기 제1 전극층에 증착된 루테늄산화물(RuOy (단, 0003c#y≤2))이 환원되고, 상기 제2 전극층에 증착된 몰리브데늄산화물(MoOz (단, 0≤z003c#2))이 산화됨으로써, 루테늄 또는 루테늄산화물(RuOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 구조를 가지는 것을 특징으로 하는,반도체 소자용 커패시터의 제조 방법. |

| 9 | 제8항에 있어서,상기 하부전극을 형성하는 단계에 포함된 상기 제1 전극층을 증착하는 단계 및 상기 제2 전극층을 증착하는 단계는,원자층 증착법(ALD), 화학증착법(CVD), 스퍼터링(sputtering), 열증착법(Thermal evaporation), 전자빔 증착법(E-beam evaporation), 분자빔 증착법(Molecular Beam Epitaxy), 펄스레이저 증착법(PLD) 중 적어도 하나를 이용하여 상기 제1 전극층 및 상기 제2 전극층을 증착하는 것을 특징으로 하는,반도체 소자용 커패시터의 제조 방법. |

| 10 | 제8항에 있어서,상기 하부전극을 형성하는 단계에 포함된 상기 제1 전극층 및 상기 제2 전극층을 열처리하는 단계는,불활성분위기, 산소분위기, 및 수소분위기 중 적어도 하나의 조건에서, 200℃ 내지 800℃ 온도로 상기 제1 전극층 및 상기 제2 전극층을 30초 내지 60분 동안 열처리하는 것을 특징으로 하는,반도체 소자용 커패시터의 제조 방법. |

| 11 | 제8항에 있어서,상기 제1 금속산화물 및 상기 제2 금속산화물은 루테늄산화물, 이리듐 산화물, 및 레늄산화물 중 적어도 하나인 것을 특징으로 하는,반도체 소자용 커패시터의 제조 방법. |

| 12 | 기판;상기 기판 상에 배치되는 트랜지스터; 및상기 트랜지스터와 전기적으로 연결되는 커패시터를 포함하고,상기 커패시터는 제1 전극층 및 제2 전극층을 포함하는 하부전극;상기 하부전극 상에 형성되는 유전체층; 및상기 유전체층 상에 형성되는 상부전극을 포함하고,상기 하부전극은 금속 또는 금속산화물(AOx (단, 0≤x003c#2))을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층으로 구성된 이중전극을 포함하고,상기 하부전극에 포함된 상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리되고, 상기 제1 전극층 및 상기 제2 전극층 사이에 산화환원반응을 통하여 형성되되,상기 이중전극은,상기 제1 전극층 및 상기 제2 전극층이 열처리됨에 따라, 상기 제1 전극층에 증착된 루테늄산화물(RuOy (단, 0003c#y≤2))이 환원되고, 상기 제2 전극층에 증착된 몰리브데늄산화물(MoOz (단, 0≤z003c#2))이 산화됨으로써, 루테늄 또는 루테늄산화물(RuOx (단, 0≤x003c#2)을 포함하는 상기 제1 전극층, 및 이산화몰리브데늄(MoO2)을 포함하는 상기 제2 전극층이 적층된 구조를 가지는 것을 특징으로 하는,디램 소자. |