| 번호 | 청구항 |

|---|---|

| 12 | 제 7 항에 있어서,상기 기판은 실리콘(Si)으로 형성되고,상기 복수의 스트립은 게르마늄(Ge)으로 형성된 것인, 반도체 소자의 제조 방법. |

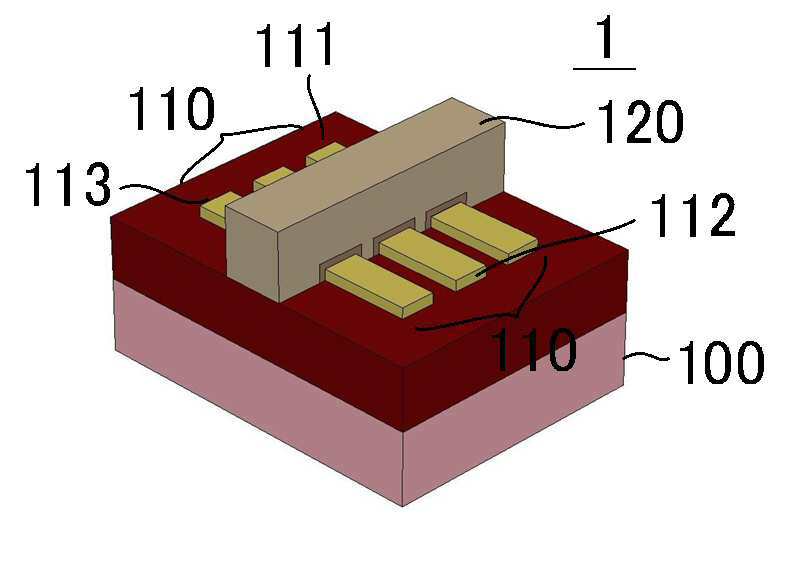

| 1 | 반도체 소자에 있어서,기판;상기 기판 상에 형성되고, 각각은 불순물이 주입되는 도핑 영역과 상기 도핑 영역 사이에 형성된 채널을 포함하는 복수의 스트립(stripes); 및상기 복수의 스트립 각각의 채널 상에 형성된 게이트(Gate)를 포함하고,상기 복수의 스트립의 도핑 영역에는 n형 불순물과 p형 불순물이 교호로 도핑되고, 상기 복수의 스트립은 도핑 영역에 p형 불순물이 도핑된 제 1 스트립;상기 제 1 스트립과 인접하고, 도핑 영역에 n형 불순물이 도핑된 제 2 스트립; 및상기 제 2 스트립에 인접하고, 도핑 영역에 p형 불순물이 도핑된 제 3 스트립을 포함하는 것인, 반도체 소자. |

| 2 | 삭제 |

| 3 | 제 1 항에 있어서,상기 게이트를 기준으로 상기 제 1 스트립의 제 1 측에 형성된 도핑 영역 및 상기 제 3 스트립의 상기 제 1 측에 형성된 도핑 영역은 소스(Source)로 동작하는 것인, 반도체 소자. |

| 4 | 제 1 항에 있어서,상기 게이트를 기준으로 상기 제 2 스트립의 제 2 측에 형성된 도핑 영역은 드레인(Drain)으로 동작하는 것인, 반도체 소자. |

| 5 | 제 1 항에 있어서,상기 반도체 소자는 터널 전계 효과 트랜지스터로 동작하는 것인, 반도체 소자. |

| 6 | 제 1 항에 있어서,상기 기판은 실리콘(Si)으로 형성되고,상기 복수의 스트립은 게르마늄(Ge)으로 형성된 것인, 반도체 소자. |

| 7 | 반도체 소자의 제조 방법에 있어서,기판 상에 복수의 스트립(stripes)을 형성하는 단계;상기 복수의 스트립의 채널 상에 게이트(Gate)를 형성하는 단계;상기 복수의 스트립에서 상기 게이트를 제외한 부분을 식각하여 불순물이 주입되는 도핑 영역을 형성하는 단계; 및상기 복수의 스트립의 도핑 영역을 n형 불순물과 p형 불순물을 교호로 도핑하는 단계를 포함하고, 상기 복수의 스트립의 도핑 영역을 n형 불순물과 p형 불순물을 교호로 도핑하는 단계는제 1 스트립의 도핑 영역에 p형 불순물을 도핑하는 단계;상기 제 1 스트립과 인접한 제 2 스트립의 도핑 영역에 n형 불순물을 도핑하는 단계; 및상기 제 2 스트립에 인접한 제 3 스트립의 도핑 영역에 p형 불순물을 도핑하는 단계를 포함하는 것인, 반도체 소자의 제조 방법. |

| 8 | 제 7 항에 있어서,상기 복수의 스트립의 채널 상에 게이트(Gate)를 형성하는 단계는상기 채널 상에 더미 게이트를 형성하는 단계;상기 복수의 스트립의 도핑 영역을 n형 불순물과 p형 불순물을 교호로 도핑하는 단계 이후에 상기 더미 게이트를 제거하는 단계;상기 복수의 스트립의 채널 상에 산화막을 형성하는 단계; 및상기 산화막 상에 메탈층을 형성하는 단계를 포함하는 것인, 반도체 소자의 제조 방법. |

| 9 | 삭제 |

| 10 | 제 7 항에 있어서,상기 게이트를 기준으로 상기 제 1 스트립의 제 1 측에 형성된 도핑 영역 및 상기 제 3 스트립의 상기 제 1 측에 형성된 도핑 영역은 소스(Source)로 동작하고,상기 게이트를 기준으로 상기 제 2 스트립의 제 2 측에 형성된 도핑 영역은 드레인(Drain)으로 동작하는 것인, 반도체 소자의 제조 방법. |

| 11 | 제 7 항에 있어서,상기 반도체 소자는 터널 전계 효과 트랜지스터로 동작하는 것인, 반도체 소자의 제조 방법. |

| 13 | 반도체 소자에 있어서,기판;스트립의 제 1 측이 소스(Source)로 동작하는 제 1 스트립;상기 제 1 스트립에 인접하고, 스트립의 제 2 측이 드레인(Drain)으로 동작하는 제 2 스트립;상기 제 2 스트립에 인접하고, 상기 스트립의 제 1 측이 소스로 동작하는 제 3 스트립; 및상기 제 1 스트립, 상기 제 2 스트립 및 상기 제 3 스트립의 채널 상에 형성된 게이트(Gate)를 포함하는 것이되, 상기 제 1 스트립, 상기 제 2 스트립 및 상기 제 3 스트립의 도핑 영역에는 n형 불순물과 p형 불순물이 교호로 도핑되고, 상기 제 1 스트립의 도핑 영역에는 p형 불순물이 도핑되고, 상기 제 2 스트립의 도핑 영역에는 n형 불순물이 도핑되고, 상기 제 3 스트립의 도핑 영역에는 p형 불순물이 도핑되는 것인, 반도체 소자. |

| 14 | 삭제 |