| 번호 | 청구항 |

|---|---|

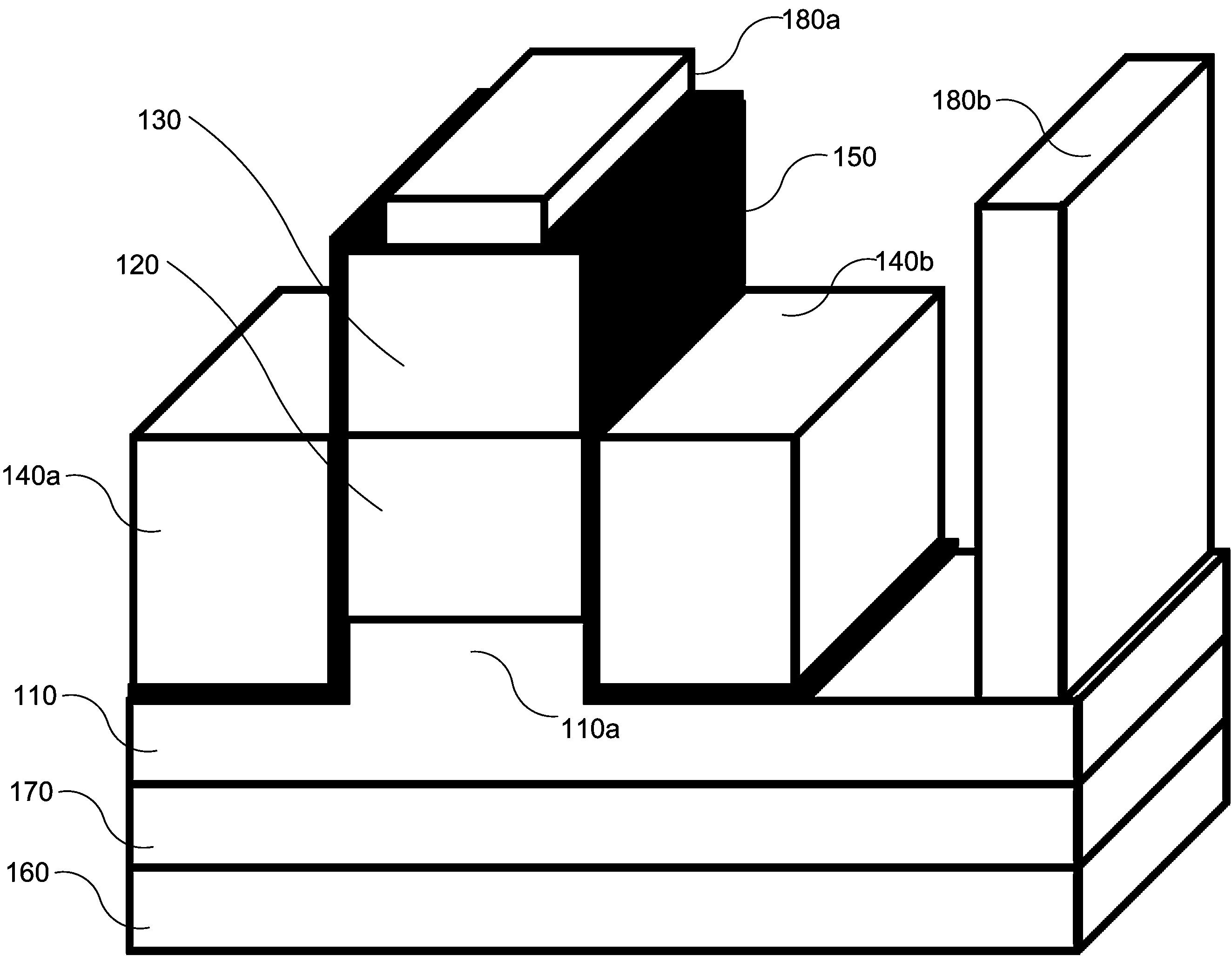

| 1 | 돌출부를 포함하는 소스 영역;상기 돌출부의 일 측에 구비되는 제1 게이트 전극;상기 돌출부의 상기 제1 게이트 전극과 대향하는 측에 구비되는 제2 게이트 전극;상기 돌출부 상에 상기 제1 게이트 전극과 상기 제2 게이트 전극의 사이에 구비되는 채널 영역;상기 채널 영역의 상부에 구비되는 드레인 영역; 및상기 채널 영역과 상기 제1 게이트 전극 및 상기 제2 게이트 전극의 경계면과, 상기 소스 영역과 상기 제1 게이트 전극 및 상기 제2 게이트 전극의 경계면과, 상기 드레인 영역 중 적어도 상기 제1 게이트 전극 및 상기 제2 게이트 전극과 대향하는 면에 구비되는 절연막을 포함하고,상기 돌출부의 두께(Tsov)와 상기 채널의 길이(Lchannel)와 상기 게이트의 길이(Lgate)는Lgate = Lchannel + Tsov의 관계를 만족하고,상기 Tsov는0.125×Lgate ≤ Tsov ≤ 0.8×Lgate의 관계를 만족하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 2 | 제1항에 있어서,상기 절연막은 상기 드레인 영역의 상면 중 적어도 일부에 구비되는 수직 구조 터널 전계 효과 트랜지스터. |

| 3 | 제1항에 있어서,상기 제1 게이트 전극, 상기 제2 게이트 전극, 상기 드레인 영역 및 상기 소스 영역에 각각 구비되는 컨택트 영역을 더 포함하는 수직 구조 터널 전계 효과 트랜지스터. |

| 4 | 제1항에 있어서,상기 소스 영역이 배치되는 기판을 더 포함하는 수직 구조 터널 전계 효과 트랜지스터. |

| 5 | 제4항에 있어서,상기 기판은 실리콘(Si) 기판, 게르마늄(Ge) 기판, 실리콘 및 게르마늄의 화합물을 포함하는 기판, III-V족 화합물을 포함하는 기판, SOI(Silicon-on-insulator) 기판, GOI(Germanium-on-insulator) 기판 및 SGOI(Silicon-Germanium-on-insulator) 기판 중 어느 하나인 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 6 | 제1항에 있어서,기판; 및상기 기판 상에 배치되는 매몰 산화막(buried oxide)을 더 포함하고,상기 소스 영역은 상기 매몰 산화막 상에 구비되는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 7 | 제6항에 있어서,상기 기판은 실리콘(Si) 기판, 게르마늄(Ge) 기판, 실리콘 및 게르마늄의 화합물을 포함하는 기판 및 III-V족 화합물을 포함하는 기판 중 어느 하나인 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 8 | 제1항에 있어서,상기 제1 게이트 전극 및 상기 제2 게이트 전극 중 적어도 하나는 폴리실리콘, 몰리브덴(Mo), 니켈(Ni), 백금(Pt), 산화 루테늄(RuO2), 티타늄(Ti), 질화티타늄(TiN), 탄탈룸(Ta) 및 질화탄탈룸(TaN)을 포함하는 그룹으로부터 선택되는 물질을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 9 | 제1항에 있어서,상기 소스 영역은 게르마늄을 포함하는 것이고,상기 드레인 영역은 실리콘을 포함하는 것이고,상기 채널 영역은 실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 10 | 제9항에 있어서,상기 소스 영역은 p-타입 불순물로 도핑되고,상기 드레인 영역은 n-타입 불순물로 도핑되는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 11 | 제10항에 있어서,상기 n-타입 불순물은 비소(As), 인(P), 비스무스(Bi) 및 안티몬(Sb) 중에서 적어도 하나를 포함하고,상기 n-타입 불순물의 도핑 농도는 1×1018/cm3 내지 1×1020/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 12 | 제10항에 있어서,상기 p-타입 불순물은 알루미늄(Al), 붕소(B), 인듐(In) 및 갈륨(Ga) 중에서 적어도 하나를 포함하고,상기 p-타입 불순물의 도핑 농도는 1×1018/cm3 내지 1×1020/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 13 | 제10항에 있어서,상기 채널 영역은 상기 p-타입 불순물 및 상기 n-타입 불순물 중 어느 하나로 도핑되는 것이고,상기 채널 영역의 도핑 농도는 1×1014/cm3 내지 1×1016/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 14 | 제10항에 있어서,상기 채널 영역은 진성(intrinsic) 실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 15 | 제10항에 있어서,상기 제1 게이트 전극 및 상기 제2 게이트 전극 중 적어도 하나는 상기 n-타입 불순물로 도핑된 폴리실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 16 | 제1항에 있어서,상기 절연막은 SiO2, Si3N4, Al2O3, HfO2, La2O3 및 ZrO2 중에서 적어도 어느 하나를 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터. |

| 17 | 삭제 |

| 18 | (a) 소스 층, 상기 소스 층 상에 구비되는 채널 층, 상기 채널 층 상에 구비되는 드레인 층을 포함하는 기판을 준비하는 단계;(b) 상기 기판을 미리 지정된 패턴을 기초로 식각하여, 상기 기판 상에 돌출부를 포함하는 소스 영역, 상기 돌출부 상에 구비되는 채널 영역 및 상기 채널 영역 상에 구비되는 드레인 영역을 형성하는 단계;(c)상기 기판 상에 절연막을 형성하는 단계; 및(d) 상기 돌출부 및 상기 채널 영역의 일 측에 제1 게이트 전극을 형성하고 상기 돌출부 및 상기 채널 영역의 상기 제1 게이트 전극과 대향하는 측에 제2 게이트 전극을 형성하는 단계를 포함하고,상기 돌출부의 두께(Tsov)와 상기 채널의 길이(Lchannel)와 상기 게이트의 길이(Lgate)는 Lgate = Lchannel + Tsov의 관계를 만족하고,상기 Tsov는 0.125×Lgate ≤ Tsov ≤ 0.8×Lgate의 관계를 만족하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 19 | 제18항에 있어서,(e) 상기 제1 게이트 전극, 상기 제2 게이트 전극, 상기 드레인 영역, 상기 소스 영역 각각과 전기적으로 연결되는 컨택트 영역을 형성하는 단계를 더 포함하는 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 20 | 제18항에 있어서,(f) 상기 단계 (d) 이후에 층간 유전막(interlayer dielectric)을 형성하는 단계를 더 포함하는 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 21 | 제18항에 있어서,상기 제1 게이트 전극 및 상기 제2 게이트 전극 중 적어도 하나는 폴리실리콘, 몰리브덴(Mo), 니켈(Ni), 백금(Pt), 산화 루테늄(RuO2), 티타늄(Ti), 질화티타늄(TiN), 탄탈룸(Ta) 및 질화탄탈룸(TaN)을 포함하는 그룹으로부터 선택되는 물질을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 22 | 제18항에 있어서,상기 소스 영역은 게르마늄을 포함하는 것이고,상기 드레인 영역은 실리콘을 포함하는 것이고,상기 채널 영역은 실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 23 | 제22항에 있어서,상기 소스 영역은 p-타입 불순물로 도핑되고,상기 드레인 영역은 n-타입 불순물로 도핑되는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 24 | 제23항에 있어서,상기 n-타입 불순물은 비소(As), 인(P), 비스무스(Bi) 및 안티몬(Sb) 중에서 적어도 하나를 포함하고,상기 n-타입 불순물의 도핑 농도는 1×1018/cm3 내지 1×1020/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 25 | 제23항에 있어서,상기 p-타입 불순물은 알루미늄(Al), 붕소(B), 인듐(In) 및 갈륨(Ga) 중에서 적어도 하나를 포함하고,상기 p-타입 불순물의 도핑 농도는 1×1018/cm3 내지 1×1020/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 26 | 제23항에 있어서,상기 채널 영역은 상기 p-타입 불순물 및 상기 n-타입 불순물 중 어느 하나로 도핑되는 것이고,상기 채널 영역의 도핑 농도는 1×1014/cm3 내지 1×1016/cm3인 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 27 | 제23항에 있어서,상기 채널 영역은 진성 실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 28 | 제23항에 있어서,상기 제1 게이트 전극 및 상기 제2 게이트 전극 중 적어도 하나는 상기 n-타입 불순물로 도핑된 폴리실리콘을 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 29 | 제18항에 있어서,상기 절연막은 SiO2, Si3N4, Al2O3, HfO2, La2O3 및 ZrO2 중에서 적어도 어느 하나를 포함하는 것인 수직 구조 터널 전계 효과 트랜지스터의 제조 방법. |

| 30 | 삭제 |