| 번호 | 청구항 |

|---|---|

| 8 | 제7 항에 있어서,상기 상부 전극 및 상기 하부 전극들은 전도성 산화물 또는 금속을 포함하는 메모리 소자. |

| 9 | 제1 항에 있어서,평면적 관점에서, 상기 수직 구조체의 형상은 사각형인 메모리 소자. |

| 10 | 삭제 |

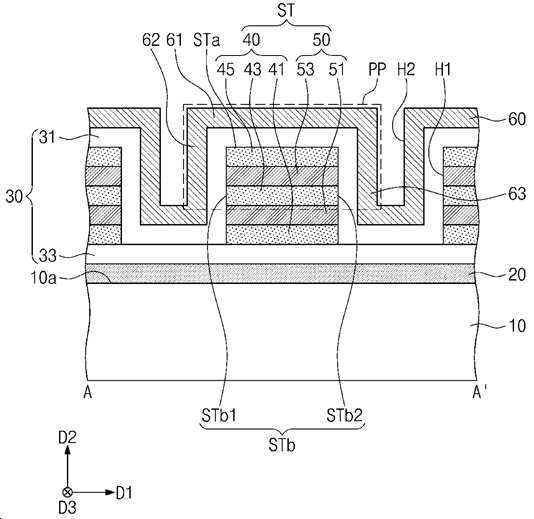

| 1 | 기판;상기 기판 상에 제공되는 복수의 수직 구조체들;상기 수직 구조체들 각각의 상면 및 측면들 상에 제공되는 상부 전극; 및상기 상부 전극 및 상기 수직 구조체들 사이에 배치되며, 상기 수직 구조체들 각각의 상면 및 측면들을 덮는 제1 유전층을 포함하되,상기 수직 구조체들은 상기 기판의 상면과 평행한 제1 방향 및 상기 제1 방향과 교차하는 제2 방향으로 정렬되며,상기 수직 구조체들 각각은 제1 절연층, 상기 제1 절연층 상에 제공되는 제1 하부 전극, 상기 제1 하부 전극 상에 제공되는 제2 절연층, 상기 제2 절연층 상에 제공되는 제2 하부 전극 및 상기 제2 하부 전극 상에 제공되는 제3 절연층을 포함하고,상기 제3 절연층은 상기 제2 하부 전극의 상면을 덮으며,상기 제1 유전층은 상기 제3 절연층의 상면 및 상기 제1 및 제2 하부 전극들의 측면들을 덮고,상기 제1 유전층은 강유전 물질을 포함하며,상기 상부 전극은 상기 기판 상의 돌출부들을 정의하는 리세스부들을 포함하고,상기 상부 전극의 수직하게 연장되는 상기 리세스부와 상기 제2 하부 전극의 상기 측면 사이에 상기 제1 유전층이 직접 개재되어 강유전체 커패시터를 구성하는 메모리 소자. |

| 2 | 제1 항에 있어서,상기 수직 구조체들 각각의 상기 측면들은 제1 측면 및 상기 제1 측면과 마주보는 제2 측면을 갖되,상기 제1 유전층은 상기 수직 구조체들 각각의 상면으로부터 상기 제1 측면 및 상기 제2 측면 상으로 연장되어, 상기 제1 측면 및 상기 제2 측면과 접촉하는 메모리 소자. |

| 3 | 제2 항에 있어서,상기 상부 전극은 상기 수직 구조체들 각각의 상면 상에 제공되는 제1 부분, 상기 제1 부분과 연결되고 상기 제1 측면 상에 제공되는 제2 부분, 및 상기 제1 부분과 연결되고 상기 제2 측면 상에 제공되는 제3 부분을 포함하되,상기 제2 부분 및 상기 제3 부분은 상기 제1 측면 및 상기 제2 측면과 각각 평행하게 연장되는 메모리 소자. |

| 4 | 제1 항에 있어서,상기 강유전 물질은 티탄산 지르콘산 납(Pb(Zr1-yTiy)O3), 비스무스 페라이트(BiFeO3), 티탄산 납(PbTiO3), 하프늄 산화물(HfO2), 또는 타이타늄산 바륨(BaTiO3)을 포함하는 메모리 소자. |

| 5 | 제1 항에 있어서,상기 기판 상에 제공되는 제2 유전층을 더 포함하되,상기 제2 유전층은 상기 수직 구조체들 각각의 하면 및 상기 기판 사이로 연장되는 메모리 소자. |

| 6 | 제5 항에 있어서,상기 수직 구조체들의 상면은 상기 제1 유전층으로 덮히고, 상기 수직 구조체들의 하면은 상기 제2 유전층으로 덮히는 메모리 소자. |

| 7 | 제1 항에 있어서상기 상부 전극은 상기 하부 전극과 다른 물질을 포함하는 메모리 소자. |

| 11 | 기판 상에 공통 절연층 및 제2 유전층을 차례로 형성하는 것;상기 제2 유전층의 상면 상에 제1 절연층, 제1 하부 전극, 제2 절연층, 제2 하부 전극 및 제3 절연층을 차례로 형성하는 것;상기 제1 절연층, 상기 제1 하부 전극, 상기 제2 절연층, 상기 제2 하부 전극 및 상기 제3 절연층 상에 식각 공정을 수행하여 상기 제2 유전층의 상면을 노출시키는 수직 구조체들을 형성하는 것;상기 제3 절연층의 상면, 상기 수직 구조체들의 측면들 및 상기 제2 유전층의 상면을 덮는 제1 유전층을 형성하는 것; 및상기 제1 유전층의 상면 프로파일을 따라 상기 제1 유전층의 상면 상에 상부 전극을 형성하는 것을 포함하되,상기 수직 구조체들은 상기 기판의 상면과 평행한 제1 방향 및 상기 제1 방향과 교차하는 제2 방향으로 정렬되며,상기 제3 절연층은 상기 제2 하부 전극의 상면을 덮으며,상기 제1 유전층은 상기 제3 절연층의 상면 및 상기 제1 및 제2 하부 전극들의 측면들을 덮고,상기 제1 유전층은 강유전 물질을 포함하며,상기 상부 전극이 상기 기판 상의 돌출부들을 정의하는 리세스부들을 포함하고,상기 상부 전극의 수직하게 연장되는 상기 리세스부와 상기 제2 하부 전극의 상기 측면 사이에 상기 제1 유전층이 직접 개재되어 강유전체 커패시터를 구성하는 메모리 소자의 제조 방법. |

| 12 | 제11 항에 있어서,상기 하부 전극들은 Cr, Ti, TiN, TaN, TiW, Co, W, LSMO, LCMO, PCMO, SrRuO3, LSCO, ITO, FTO, YBCO, RuO2, 및 LaNiO3 중 어느 하나를 포함하고,상기 상부 전극은 Au, Pt, Pd, Ag, Cu 및 Ni 중 어느 하나를 포함하는 메모리 소자의 제조 방법. |

| 13 | 제11 항에 있어서,상기 수직 구조체들을 형성하는 것은 상기 하부 전극들 및 상기 절연층들의 일부를 제거하여 제1 식각부를 형성하는 것을 포함하되,상기 식각 공정은 제2 유전층의 상면이 노출될 때까지 수행되고,상기 제1 식각부는 상기 수직 구조체들을 정의하는 메모리 소자의 제조 방법. |

| 14 | 제11 항에 있어서,상기 제1 유전층의 상면 프로파일을 따라 상기 제1 유전층의 상면 상에 상기 상부 전극을 증착시키는 것은 전자빔 증착법, 열 기화법, 레이저 증착법, 스퍼터링 증착법, 기상화학 증착법, 또는 분자층 증착법을 이용하여 수행되는 메모리 소자의 제조 방법. |

| 15 | 제11 항에 있어서,상기 강유전 물질은 티탄산 지르콘산 납(Pb(Zr1-yTiy)O3), 비스무스 페라이트(BiFeO3), 티탄산 납(PbTiO3), 하프늄 산화물(HfO2), 또는 타이타늄산 바륨(BaTiO3)을 포함하는 메모리 소자의 제조 방법. |

| 16 | 제11 항에 있어서,상기 상부 전극을 증착시킨 후, 상기 상부 전극에 열처리 공정을 수행하는 것을 더 포함하는 메모리 소자의 제조 방법. |