| 번호 | 청구항 |

|---|---|

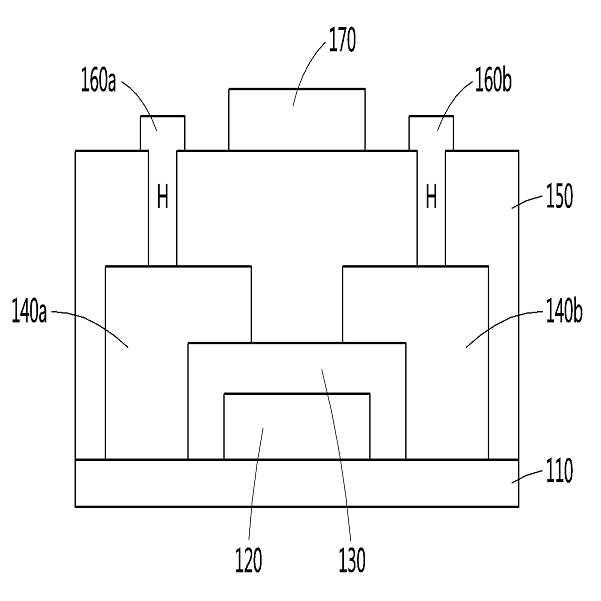

| 1 | 기판 상에 형성되는 제1 게이트 전극;상기 제1 게이트 전극 상에 형성되는 산화물 반도체층;상기 산화물 반도체층 일측에 형성되는 소스/드레인 전극;상기 소스/드레인 전극 상에 형성되는 게이트 절연막;상기 게이트 절연막의 일측에 관통하여 형성되는 컨택홀을 통하여 상기 소스/드레인 전극과 전기적으로 연결되는 소스/드레인 전극 패드; 및상기 게이트 절연막 상에 형성되는 제2 게이트 전극을 포함하고,상기 산화물 반도체층은 상기 소스/드레인 전극 및 상기 제1 게이트 전극 사이에 형성되는 전도성 필라멘트의 제어에 기반한 저항 변화형 스위칭층으로 구동하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 2 | 제1항에 있어서,상기 저항 변화형 스위칭층은, 상기 전도성 필라멘트의 수가 조절되어 상기 저항 변화형 스위칭층의 저항 상태를 제어하고, 상기 제어된 저항 상태에 의해 드레인 전류의 크기를 다단계로 제어하여 멀티레벨 메모리층으로 동작 하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 3 | 제2항에 있어서,상기 소스/드레인 전극은 각각 접지 상태를 유지하면서, 상기 제1 게이트 전극에는 프로그램 전압이 인가되어 상기 산화물 반도체층 내의 상기 전도성 필라멘트의 수가 제어되는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 4 | 제1항에 있어서,상기 저항 변화형 메모리 트랜지스터는,상기 산화물 반도체층 상부에 상기 산화물 반도체층의 물리적 또는 화학적 손상을 방지하고, 구동 특성을 개선시키는 보호 절연막을 더 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 5 | 제4항에 있어서,상기 저항 변화형 스위칭층은,상기 보호 절연막 및 상기 산화물 반도체층으로 형성되는 적층 구조인 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 6 | 제4항에 있어서,상기 보호 절연막은 실리콘 산화막(SiO2), 실리콘 질화막(SiN), 실리콘산질화막(SiON), 알루미늄 산화막(Al2O3), 하프늄 산화막(HfO2), 지르코늄 산화막(ZrO2), 마그네슘 산화막(MgO), 티타늄 산화막(TiO2), 탄탈륨 산화막(Ta2O5), 란타늄 산화막(La2O3) 및 스트론튬-티타늄 산화막(SrTiO3) 중 적어도 하나를 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 7 | 기판 상에 형성되는 제1 게이트 전극;상기 제1 게이트 전극 상에 형성되는 산화물 반도체층;상기 산화물 반도체층 일측에 형성되고, 적어도 2개 이상의 층을 포함하는 적층 구조의 소스/드레인 전극;상기 적층 구조의 소스/드레인 전극 상에 형성되는 게이트 절연막;상기 게이트 절연막 일측에 관통하여 형성되는 컨택홀을 통하여 상기 적층 구조의 소스/드레인 전극과 전기적으로 연결되는 소스/드레인 전극 패드; 및상기 게이트 절연막 상에 형성되는 제2 게이트 전극을 포함하고,상기 산화물 반도체층은 상기 적층 구조의 소스/드레인 전극 및 상기 제1 게이트 전극 사이에 형성되는 전도성 필라멘트의 제어에 기반한 저항 변화형 스위칭층으로 구동하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 8 | 제7항에 있어서,상기 저항 변화형 메모리 트랜지스터는,상기 산화물 반도체층 상부에 상기 산화물 반도체층의 물리적 또는 화학적 손상을 방지하고, 구동 특성을 개선시키는 보호 절연막을 더 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 9 | 제8항에 있어서,상기 저항 변화형 스위칭층은,상기 보호 절연막 및 상기 산화물 반도체층으로 형성되는 적층 구조인 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 10 | 제7항에 있어서,상기 적층 구조의 소스/드레인 전극 중 최상단 소스/드레인 전극은,식각액에 대한 열화를 최소화하는 전도성 산화물을 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 11 | 제10항에 있어서,상기 전도성 산화물은 ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide) 및 AZO (Aluminum Zinc Oxide) 중 적어도 하나를 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 12 | 기판 상에 형성되는 제1 게이트 전극;상기 제1 게이트 전극 상에 형성되는 게이트 절연막;상기 게이트 절연막의 일측에 형성되는 소스/드레인 전극;상기 게이트 절연막 및 소스/드레인 전극 상에 형성되는 산화물 반도체층; 및상기 산화물 반도체층 상에 형성되는 제2 게이트 전극을 포함하고,상기 산화물 반도체층은 상기 소스/드레인 전극 및 상기 제2 게이트 전극 사이에 형성되는 전도성 필라멘트의 제어에 기반한 저항 변화형 스위칭층으로 구동하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 13 | 제12항에 있어서,상기 저항 변화형 메모리 트랜지스터는,상기 산화물 반도체층 상부에 상기 산화물 반도체층의 물리적 또는 화학적 손상을 방지하고, 구동 특성을 개선시키는 보호 절연막을 더 포함하는 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |

| 14 | 제13항에 있어서,상기 저항 변화형 스위칭층은,상기 보호 절연막 및 상기 산화물 반도체층으로 형성되는 적층 구조인 것을 특징으로 하는 저항 변화형 메모리 트랜지스터. |