| 번호 | 청구항 |

|---|---|

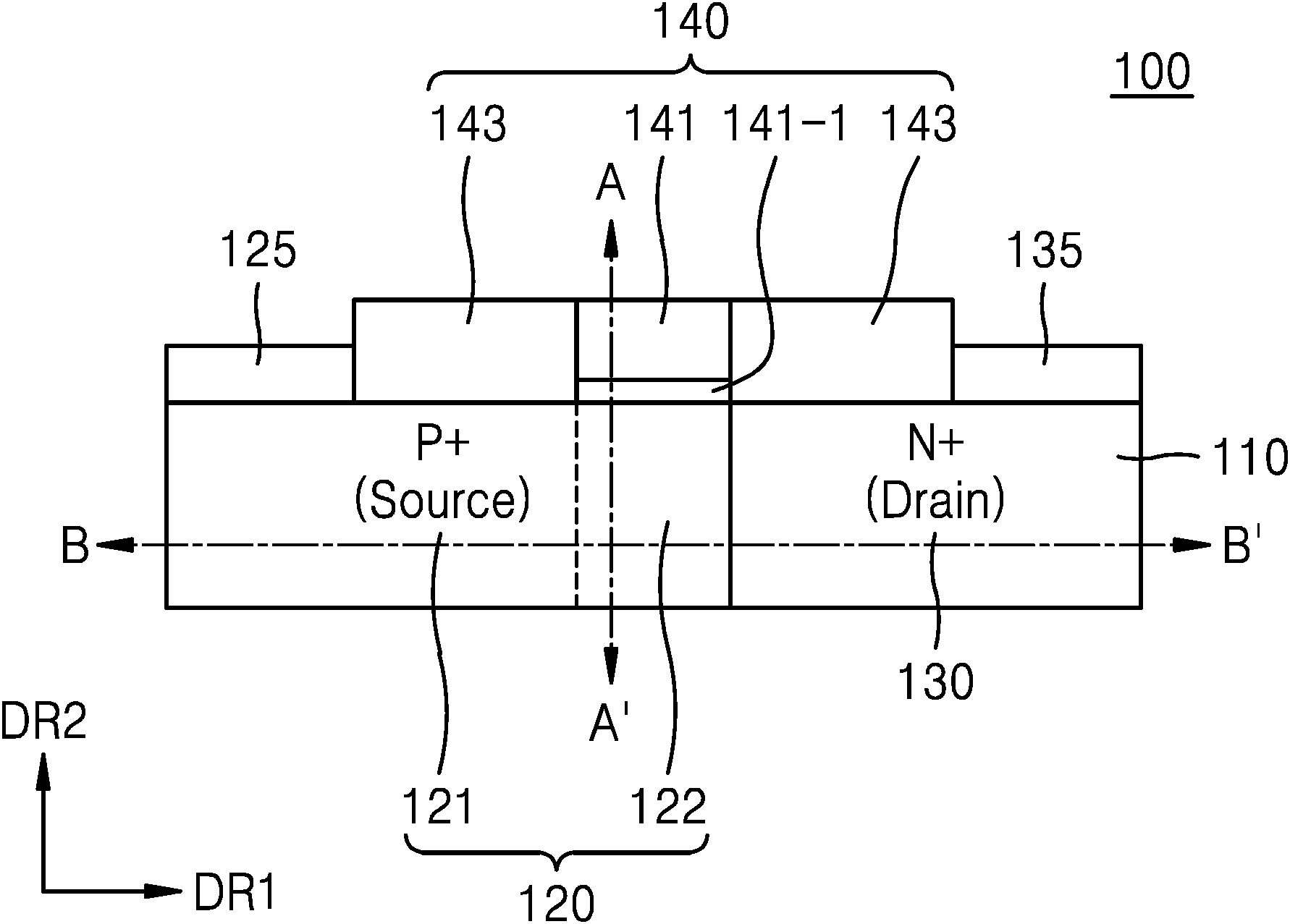

| 1 | 기판 상에 구비되며 제1 도전형 반도체 영역 및 상기 제1 도전형 반도체 영역과 상이한 도전형을 갖고 상기 제1 도전형 반도체 영역과 접하는 제2 도전형 반도체 영역; 상기 제1 도전형 반도체 영역 상에 제공되는 적어도 하나의 게이트 전극; 및상기 적어도 하나의 게이트 전극과 상기 제1 도전형 반도체 영역 사이에 개재되는 적어도 하나의 게이트 절연막;을 포함하며, 상기 제1 도전형 반도체 영역은 적어도 일부분이 상기 적어도 하나의 게이트 절연막과 접하고 적어도 일부분이 상기 제2 도전형 반도체 영역과 접하는 고농도 무접합 도핑 영역을 포함하며,상기 고농도 무접합 도핑 영역은 다수 반송자(majority carrier)가 축퇴 상태(degenerate state)로 있는 영역이므로 pn 접합을 구성하지 않으며, 상기 적어도 하나의 게이트 전극으로부터 인가되는 게이트 전계에 의해 상기 고농도 무접합 도핑 영역 내에 수직 방향의 밴드 휨에 따라 밴드간 터널링 전류가 형성되는, 트랜지스터. |

| 2 | 제1항에 있어서,상기 트랜지스터는 소스 컨택 메탈; 을 더 포함하며, 상기 제1 도전형 반도체 영역은 상기 소스 컨택 메탈과 접촉하는 소스 영역을 더 포함하며, 상기 소스 영역과 상기 고농도 무접합 도핑 영역은 동일한 도전형을 가지고 일체로 구비된, 트랜지스터. |

| 3 | 제2항에 있어서,상기 적어도 하나의 게이트 전극은,상기 소스 영역에 인접하게 배치되는 보조 게이트 전극; 및상기 보조 게이트 전극과 이격된 조절 게이트 전극;을 포함하는, 트랜지스터. |

| 4 | 제3항에 있어서,상기 보조 게이트 전극 및 상기 조절 게이트 전극은 각각 설정치 이상의 일함수를 갖는 물질로 형성되는, 트랜지스터. |

| 5 | 제4항에 있어서,상기 보조 게이트 전극의 일함수 및 상기 조절 게이트 전극의 일함수 간의 차이는 설정된 크기 이상인, 트랜지스터. |

| 6 | 3진 신호를 출력하는 인버터로서,전원 전압과 접지 단자 사이에 직렬 접속된 제1 트랜지스터 및 제2 트랜지스터를 포함하고,상기 제1 트랜지스터 및 상기 제2 트랜지스터는,기판 상에 구비되며 제1 도전형 반도체 영역 및 상기 제1 도전형 반도체 영역과 상이한 도전형을 갖고 상기 제1 도전형 반도체 영역과 접하는 제2 도전형 반도체 영역; 상기 제1 도전형 반도체 영역 상에 제공되는 적어도 하나의 게이트 전극; 및상기 적어도 하나의 게이트 전극과 상기 제1 도전형 반도체 영역 사이에 개재되는 적어도 하나의 게이트 절연막;을 포함하며, 상기 제1 도전형 반도체 영역은 적어도 일부분이 상기 적어도 하나의 게이트 절연막과 접하고 적어도 일부분이 상기 제2 도전형 반도체 영역과 접하는 고농도 무접합 도핑 영역을 포함하며,상기 고농도 무접합 도핑 영역은 다수 반송자(majority carrier)가 축퇴 상태(degenerate state)로 있는 영역인, 인버터. |

| 7 | 제6항에 있어서,상기 인버터는,상기 제1 트랜지스터 및 상기 제2 트랜지스터 각각에 대해, PN 접합의 밴드간 터널링에 의한 게이트 전압에 무관한 오프(OFF) 상태의 정전류에 기초하여 상기 3진 신호를 출력시키는, 인버터. |

| 8 | 제6항에 있어서,상기 트랜지스터는 소스 컨택 메탈; 을 더 포함하며, 상기 제1 도전형 반도체 영역은 상기 소스 컨택 메탈과 접촉하는 소스 영역을 더 포함하며, 상기 소스 영역과 상기 고농도 무접합 도핑 영역은 동일한 도전형을 가지고 일체로 구비된, 인버터. |

| 9 | 제8항에 있어서,상기 적어도 하나의 게이트 전극은,상기 소스 영역에 인접하게 배치되는 보조 게이트 전극; 및상기 보조 게이트 전극과 이격된 조절 게이트 전극;을 포함하는, 인버터. |

| 10 | 제9항에 있어서,상기 보조 게이트 전극 및 상기 조절 게이트 전극은 각각 설정치 이상의 일함수를 갖는 물질로 형성되는, 인버터. |

| 11 | 제10항에 있어서,상기 보조 게이트 전극의 일함수 및 상기 조절 게이트 전극의 일함수 간의 차이는 설정된 크기 이상인, 인버터. |