| 번호 | 청구항 |

|---|---|

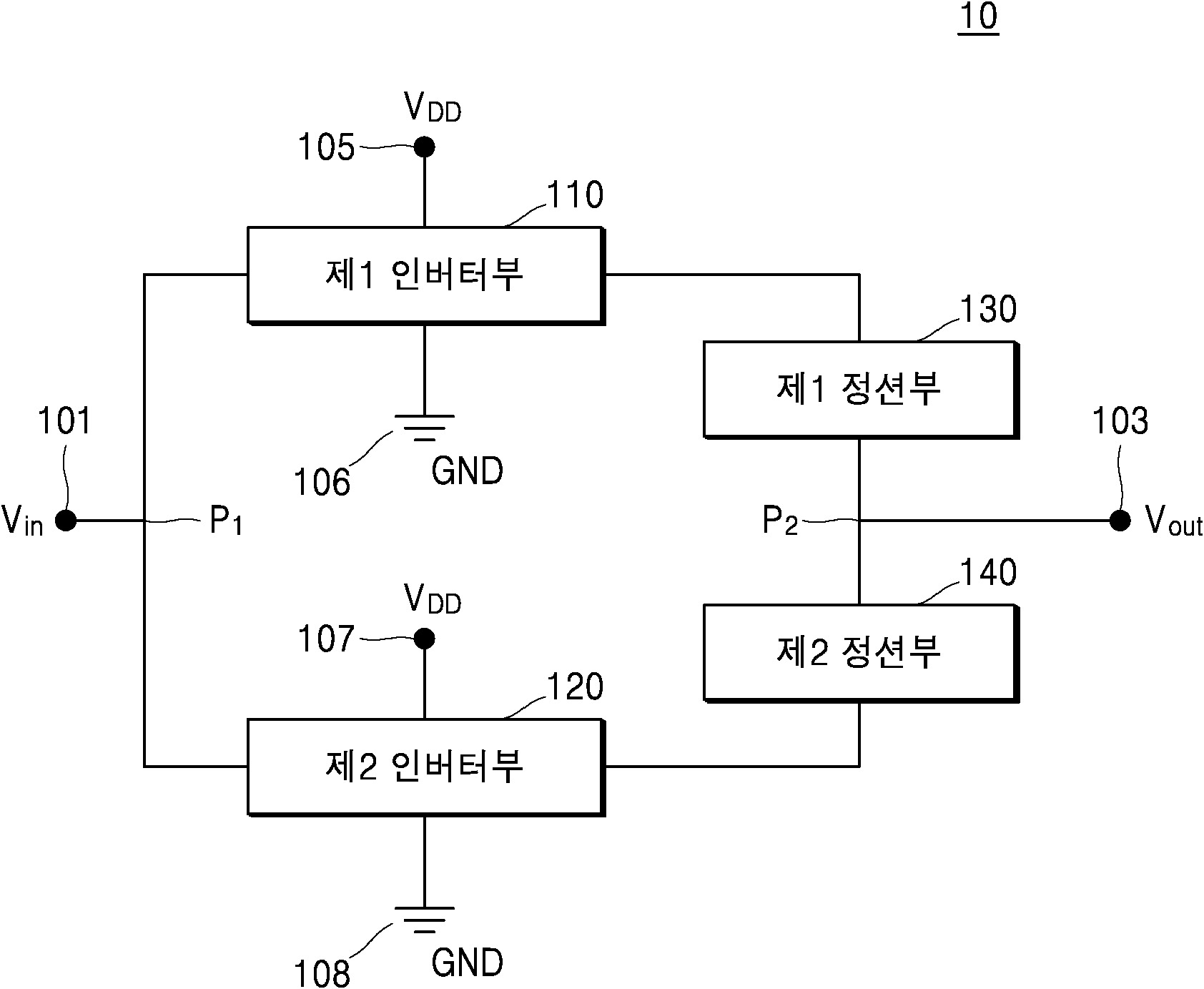

| 1 | 입력 단자 및 출력 단자와 전기적으로 연결되는, 제1 인버터부;상기 입력 단자 및 출력 단자와 전기적으로 연결되고, 상기 제1 인버터부와 병렬로 배치되는, 제2 인버터부;상기 제1 인버터부와 상기 출력 단자 사이에 배치되고, 터널 PN 정션을 포함하는, 제1 정션부; 및상기 제2 인버터부와 상기 출력 단자 사이에 배치되고, 터널 PN 정션을 포함하는, 제2 정션부;를 포함하고,상기 입력 단자에 인가되는 입력 전압의 절대값이 제1 입력 전압보다 작을 때, 상기 출력 단자는 제1 출력 전압을 출력하고, 상기 입력 전압의 절대값이 상기 제1 입력 전압보다 크고 제2 입력 전압보다 작을 때, 상기 제1 정션부 및 상기 제2 정션부는 터널링 전류를 이용하여 전압을 분배하여 상기 출력 단자는 제2 출력 전압을 출력하고, 상기 입력 전압의 절대값이 상기 제2 입력 전압보다 클 때, 상기 출력 단자는 제3 출력 전압을 출력하는, 3진수 논리회로. |

| 2 | 제1항에 있어서,상기 제1 인버터부는 제1 문턱전압을 갖는 제1 트랜지스터, 및 상기 제1 트랜지스터와 병렬로 배치되고, 제2 문턱전압을 갖는 제2 트랜지스터를 포함하고,상기 제2 인버터부는 제3 문턱전압을 갖는 제3 트랜지스터와, 상기 제3 트랜지스터와 병렬로 배치되고, 제4 문턱전압을 갖는 제4 트랜지스터를 포함하고,상기 제1 트랜지스터와 상기 제3 트랜지스터는 p형 채널을 갖고, 상기 제2 트랜지스터와 상기 제4 트랜지스터는 n형 채널을 갖는, 3진수 논리회로. |

| 3 | 제2항에 있어서,상기 제1 문턱전압의 절대값과 상기 제4 문턱전압의 절대값이 같고,상기 제2 문턱전압의 절대값과 상기 제3 문턱전압의 절대값이 같은, 3진수 논리회로. |

| 4 | 제2항에 있어서,상기 제1 트랜지스터, 제2 트랜지스터, 제3 트랜지스터 및 제4 트랜지스터는 탄소나노튜브 트랜지스터인, 3진수 논리회로. |

| 5 | 제4항에 있어서,상기 제1 트랜지스터와 상기 제4 트랜지스터는 제1 직경을 갖는 탄소나노튜브를 포함하고,상기 제2 트랜지스터와 상기 제3 트랜지스터는 제2 직경을 갖는 탄소나노튜브를 포함하고,상기 제1 직경은 상기 제2 직경보다 작은, 3진수 논리회로. |

| 6 | 제1항에 있어서,상기 제1 정션부 및 제2 정션부는 탄소나노튜브 터널 PN 정션을 포함하는, 3진수 논리회로. |

| 7 | 제6항에 있어서,상기 탄소나노튜브 터널 PN 정션에 인가되는 전기장은 1 MV/cm 이상인, 3진수 논리회로. |

| 8 | 제6항에 있어서,상기 탄소나노튜브 터널 PN 정션은 n형 도판트로 도핑된 제1 영역과, p형 도판트로 도핑된 제2 영역을 갖는, 3진수 논리회로. |

| 9 | 제8항에 있어서,상기 탄소나노튜브 터널 PN 정션은 적어도 3Х1018 원자/cm3으로 도핑된, 3진수 논리회로. |

| 10 | 삭제 |

| 11 | 제1항에 있어서,상기 제1 출력 전압은 동작 전압(Vdd)과 동일한 크기를 갖고,상기 제2 출력 전압은 상기 동작 전압의 절반(Vdd/2)의 크기를 갖고,상기 제3 출력 전압은 접지 전압과 동일한 크기를 갖는, 3진수 논리회로. |

| 12 | 제1 동작 전극, 제1 공통 전극, 및 상기 제1 동작 전극과 상기 제1 공통 전극 사이에 개재되는 제1 탄소나노튜브 채널을 포함하는, 제1 트랜지스터부;상기 제1 트랜지스터부와 상기 제1 공통 전극을 공유하고, 제1 접지 전극, 및 상기 제1 공통 전극과 상기 제1 접지 전극 사이에 개재되는 제2 탄소나노튜브 채널을 포함하는, 제2 트랜지스터부;제2 동작 전극, 제2 공통 전극, 및 상기 제2 동작 전극과 상기 제2 공통 전극 사이에 개재되는 제3 탄소나노튜브 채널을 포함하는, 제3 트랜지스터부;상기 제3 트랜지스터부와 상기 제2 공통 전극을 공유하고, 제2 접지 전극, 및 상기 제2 공통 전극과 상기 제2 접지 전극 사이에 개재되는 제4 탄소나노튜브 채널을 포함하는 제4 트랜지스터부;입력 단자와 전기적으로 연결되고, 상기 제1 탄소나노튜브 채널, 제2 탄소나노튜브 채널, 제3 탄소나노튜브 채널, 및 제4 탄소나노튜브 채널의 일부 영역 상에 배치되는, 게이트 전극;출력 단자와 전기적으로 연결되는 출력 전극;상기 제1 공통 전극 및 상기 출력 전극과 전기적으로 연결되고, 상기 제1 공통 전극과 인접하며 p형 도판트로 도핑되는 제1 영역 및 상기 출력 전극과 인접하며 n형 도판트로 도핑되는 제2 영역을 갖는 제1 탄소나노튜브 정션; 및상기 제2 공통 전극 및 상기 출력 전극과 전기적으로 연결되고, 상기 출력 전극과 인접하며 p형 도판트로 도핑되는 제3 영역 및 상기 제2 공통 전극과 인접하며 n형 도판트로 도핑되는 제4 영역을 갖는 제2 탄소나노튜브 정션;을 포함하는, 3진수 논리회로. |

| 13 | 제12항에 있어서,상기 제1 탄소나노튜브 채널과, 상기 제4 탄소나노튜브 채널은 제1 직경을 갖는 탄소나노튜브를 포함하고,상기 제2 탄소나노튜브 채널과, 상기 제3 탄소나노튜브 채널은 제2 직경을 갖는 탄소나노튜브를 포함하고, 상기 제1 직경은 상기 제2 직경보다 작은, 3진수 논리회로. |

| 14 | 제12항에 있어서,상기 제1 탄소나노튜브 채널과 상기 제3 탄소나노튜브 채널은 p형 탄소나노튜브를 포함하고,상기 제2 탄소나노튜브 채널과 상기 제4 탄소나노튜브 채널은 n형 탄소나노튜브를 포함하는, 3진수 논리회로. |

| 15 | 삭제 |

| 16 | 제12항에 있어서,상기 제1 탄소나노튜브 정션 및 제2 탄소나노튜브 정션은 적어도 3Х1018 원자/cm3으로 도핑된, 3진수 논리회로. |