| 번호 | 청구항 |

|---|---|

| 11 | 프로세서에 의해 실행 가능한 컴퓨터 프로그램 명령어들을 포함하는 컴퓨터 판독 가능한 기록매체에 기록된 시나리오 생성을 위한 컴퓨터 프로그램으로서, 컴퓨팅 장치의 프로세서에 의해 실행되는 경우에 컴퓨팅 장치로 하여금,실제 낸드플래시의 P/E 사이클에 따른 비트 오류율을 측정한 측정 데이터를 수집하는 과정; 상기 측정 데이터에서 샘플을 추출하여 P/E 사이클 당 비트 오류율에 대한 확률 모델을 구축하는 과정;상기 확률 모델을 참조하여, 가상 낸드플래시의 페이지에서 쓰기 작업이 수행되는 경우, 해당 P/E 사이클에 따른 비트 오류율을 기반으로 상기 가상 낸드플래시에 비트 오류를 삽입하는 과정; 상기 가상 낸드플래시의 P/E 사이클에 따른 비트 오류율을 측정하고, 상기 낸드플래시의 P/E 사이클에 따른 비트 오류율과의 유사성을 비교하는 과정; 및상기 유사성이 일정 수준 이하인 경우, 상기 측정 데이터에서 추가로 샘플을 추출하여 상기 확률 모델을 재구축하는 과정을 수행하도록 하는 명령어들을 포함하는 컴퓨터 프로그램. |

| 1 | 삭제 |

| 2 | 삭제 |

| 3 | 삭제 |

| 4 | 삭제 |

| 5 | 삭제 |

| 6 | 삭제 |

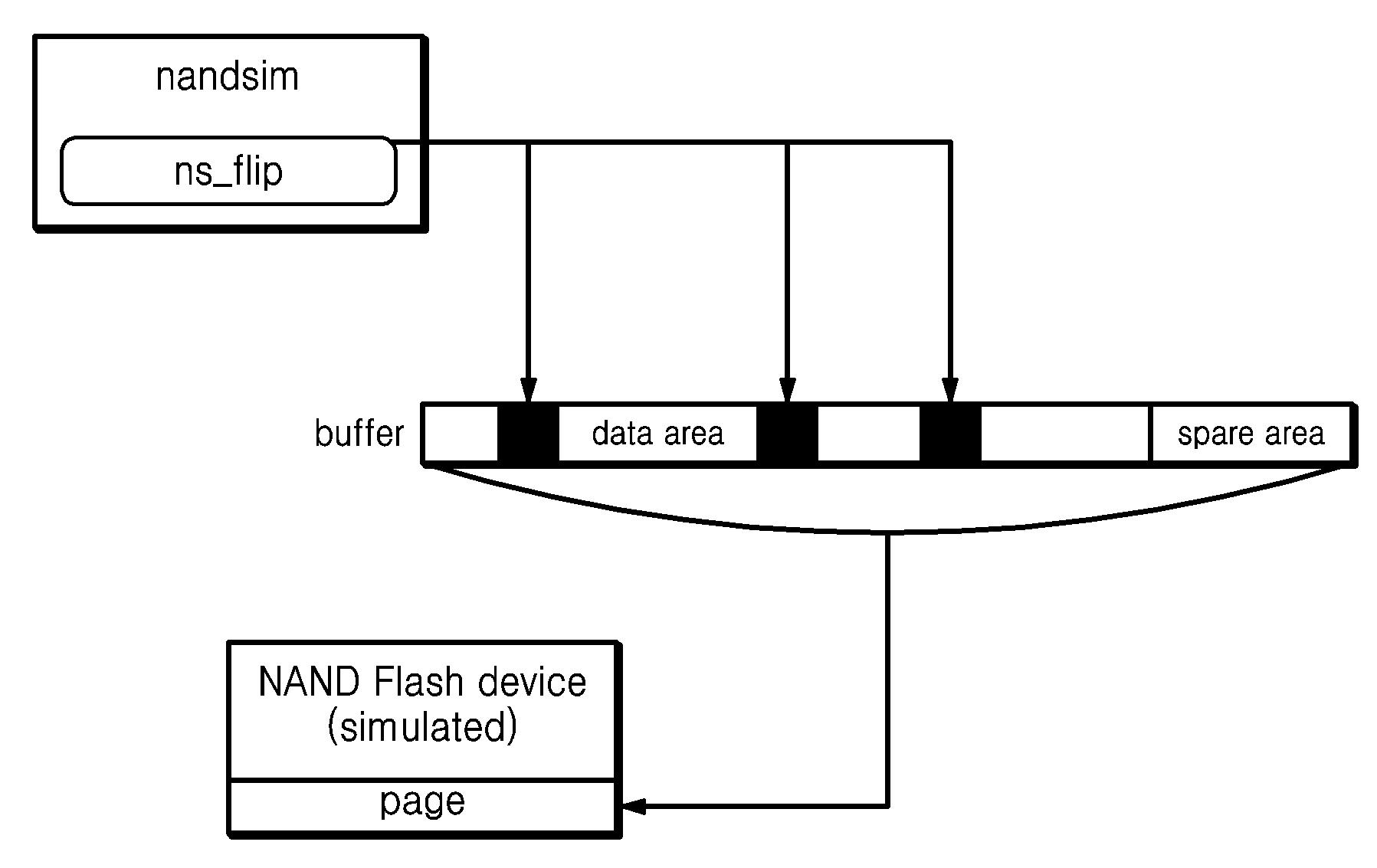

| 7 | P/E 사이클의 증가에 따라 비트 오류가 발생하는 가상 낸드플래시 구현 방법에 있어서,실제 낸드플래시의 P/E 사이클에 따른 비트 오류율을 측정한 측정 데이터를 수집하는 과정; 상기 측정 데이터에서 샘플을 추출하여 P/E 사이클 당 비트 오류율에 대한 확률 모델을 구축하는 과정;상기 확률 모델을 참조하여, 상기 가상 낸드플래시의 페이지에서 쓰기(Program) 작업이 수행되는 경우, 해당 P/E 사이클에 따른 비트 오류율을 기반으로 상기 가상 낸드플래시에 비트 오류를 삽입하는 과정; 상기 가상 낸드플래시의 P/E 사이클에 따른 비트 오류율을 측정하고, 상기 측정 데이터와 유사성을 비교하는 과정; 및상기 유사성이 일정 수준 이하인 경우, 상기 측정 데이터에서 추가로 샘플을 추출하여 상기 확률 모델을 재구축하는 과정을 포함하는 가상 낸드플래시 구현 방법. |

| 8 | 제 7항에 있어서,상기 확률 모델을 구축하는 과정은,각 샘플 사이에서의 비트 오류 발생은 선형보간법을 이용해 비트 오류율을 산정하는 것을 특징으로 하는 가상 낸드플래시 구현 방법. |

| 9 | 제 7항에 있어서,상기 확률 모델을 재구축하는 과정은,상기 유사성이 일정 수준 이하인 P/E 사이클 구간에 대해 상기 측정 데이터에서 추가로 샘플을 추출하는 것을 특징으로 하는 가상 낸드플래시 구현 방법. |

| 10 | 삭제 |