| 번호 | 청구항 |

|---|---|

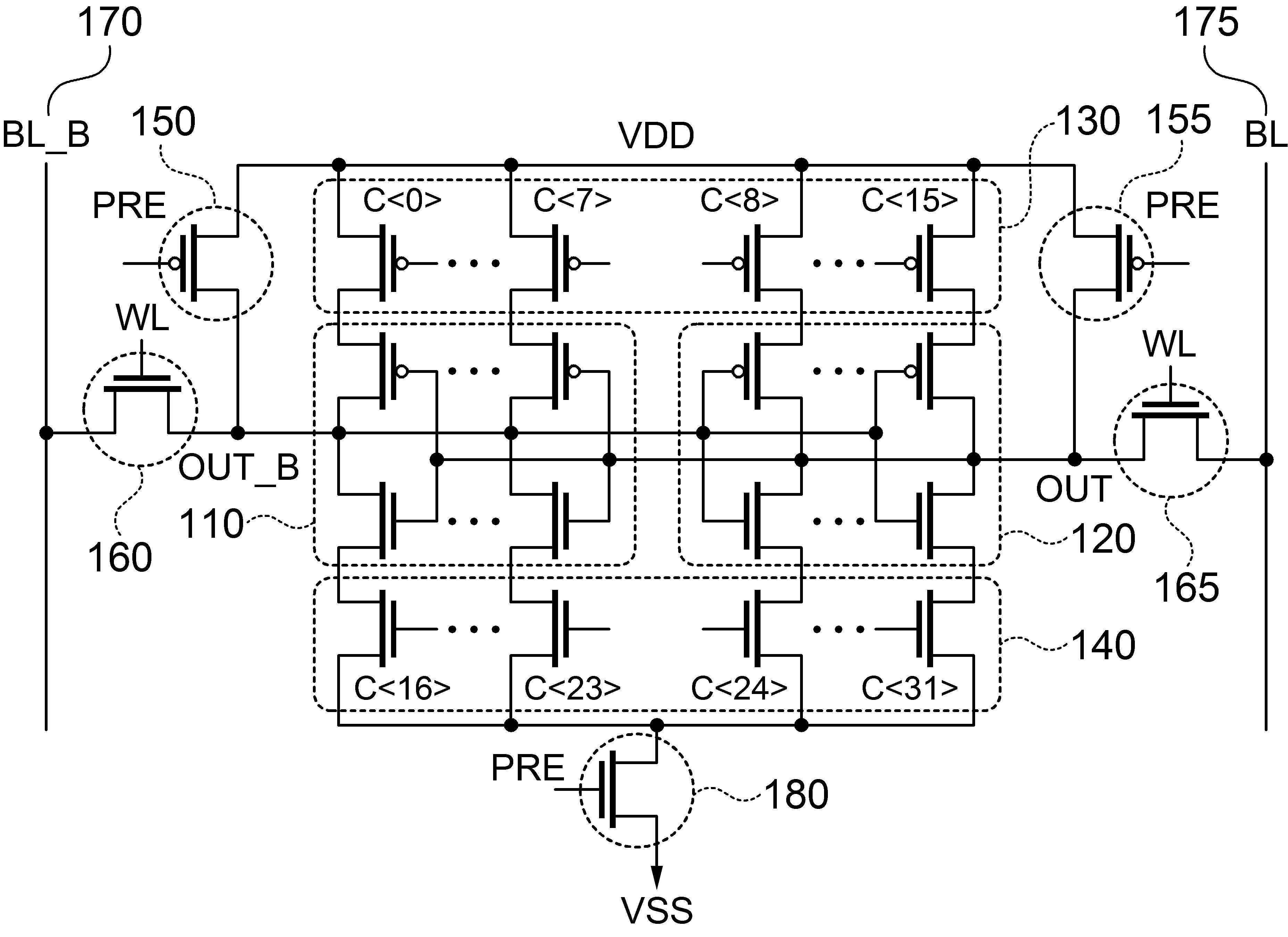

| 1 | 입력되는 챌린지 신호에 대한 응답 신호를 생성하는 퍼프 어레이를 포함하는 디지털 난수 생성 장치에 있어서,상기 퍼프 어레이 내의 퍼프 셀은, 제1 인버터부 및 제2 인버터부를 포함하고, 상기 제1 인버터부의 출력은 상기 제2 인버터부의 입력에 연결되고, 상기 제1 인버터부의 입력은 상기 제2 인버터부의 출력에 연결되어, 서로 교차 결합되고,상기 디지털 난수 생성 장치가 평가 모드로 진입하기 전에, 상기 제1 인버터부와 상기 제2 인버터부에 챌린지 신호가 입력되어 상기 디지털 난수 생성 장치의 동작 특성이 재구성되도록 하며, 상기 챌린지 신호에 대한 응답 신호를 생성하는, 디지털 난수 생성 장치. |

| 2 | 제1항에 있어서,상기 제1 인버터부 및 상기 제2 인버터부 각각은, 상호 간에 병렬 접속되는 복수의 인버터를 포함하는, 디지털 난수 생성 장치. |

| 3 | 제1항에 있어서,상기 챌린지 신호에 따라 VDD 풀업 경로가 설정되고, 상기 챌린지 신호가 상기 제1 인버터부 및 상기 제2 인버터부에 포함된 트랜지스터의 바디 전압으로 인가되도록 구성된 제1 스위칭부; 및상기 챌린지 신호에 따라 VSS 풀다운 경로가 설정되고, 상기 챌린지 신호가 상기 제1 인버터부 및 상기 제2 인버터부에 포함된 트랜지스터의 바디 전압으로 인가되도록 구성된 제2 스위칭부를 더 포함하는, 디지털 난수 생성 장치. |

| 4 | 제3항에 있어서,제2 스위칭부와 연결되며, 상기 디지털 난수 생성 장치가 리셋 모드로 동작하는 동안 상기 제1 인버터부 및 상기 제2 인버터부로 전원이 인가되지 않도록 하고, 상기 디지털 난수 생성 장치가 상기 평가 모드로 진입하면, 상기 제1 인버터부 및 상기 제2 인버터부로 전원이 인가되도록 하는 제3 스위칭부를 더 포함하는, 디지털 난수 생성 장치. |

| 5 | 제4항에 있어서,상기 제3 스위칭부는 NMOS 및 PMOS 중 적어도 하나 또는 둘 이상의 조합으로 구성된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 6 | 제1항에 있어서,상기 챌린지 신호는, 상기 제1 인버터부로 입력되는 제1 챌린지 신호 및 상기 제2 인버터부로 입력되는 제2 챌린지 신호로 구성되며,상기 제1 챌린지 신호에 의해 상기 제1 인버터부에서 선택된 인버터, 및 상기 제2 챌린지 신호에 의해 상기 제2 인버터부에서 선택된 인버터 간의 조합에 따라 상기 디지털 난수 생성 장치의 동작 특성이 재구성되어, 복수의 챌린지 응답 쌍이 형성되는 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 7 | 제1항에 있어서,상기 제1 인버터부 및 상기 제2 인버터부는,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃 상에 미리 설정된 기준선을 중심으로 대칭적으로 배치되는 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 8 | 제7항에 있어서,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부를 구성하는 트랜지스터들 및 상기 제2 인버터부를 구성하는 트랜지스터들이 상기 기준선을 중심으로 대칭적으로 배치된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 9 | 제7항에 있어서,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부의 동작과 관련된 사전 충전 트랜지스터와 상기 제2 인버터부의 동작과 관련된 사전 충전 트랜지스터는 상기 기준선을 중심으로 대칭적으로 배치된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 10 | 제9항에 있어서,상기 퍼프 어레이 내의 퍼프 셀은,상기 평가 모드에서 PRE 신호가 상기 제1 인버터부 및 상기 제2 인버터부에 상기 기준선 또는 기준점을 중심으로 대칭적으로 동시에 인가되도록 레이아웃 된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 11 | 제7항에 있어서,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부의 동작과 관련된 워드 라인과 상기 제2 인버터부의 동작과 관련된 워드 라인은, 상기 기준선을 중심으로 대칭적으로 배치된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 12 | 제7항에 있어서,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부로 챌린지 신호를 인가하기 위한 신호선과 상기 제2 인버터부로 챌린지 신호를 인가하기 위한 신호선은, 상기 기준선을 기준으로 대칭적으로 배치된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 13 | 제7항에 있어서,상기 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부의 인버터 어레이 및 상기 제2 인버터부의 인버터 어레이의 각 측면에 더미 열이 추가된 것을 특징으로 하는, 다지털 난수 생성 장치. |

| 14 | 제1항에 있어서,상기 제1 인버터부에 포함되는 인버터들과 상기 제2 인버터부에 포함되는 인버터들은 동일한 공정에서 제조되며, 상기 디지털 난수 생성 장치의 동작 특성은 공정상의 오차에 기인하는, 디지털 난수 생성 장치. |

| 15 | 입력되는 챌린지 신호에 대한 응답 신호를 생성하는 퍼프 어레이; 및상기 퍼프 어레이를 동작시키기 위한 인에이블 신호를 생성하여 상기 퍼프 어레이로 입력하는 제어기를 포함하는 디지털 난수 생성 장치에 있어서,상기 퍼프 어레이 내의 퍼프 셀은, 제1 인버터부 및 제2 인버터부를 포함하고, 상기 제1 인버터부의 출력은 상기 제2 인버터부의 입력에 연결되고, 상기 제1 인버터부의 입력은 상기 제2 인버터부의 출력에 연결되어, 서로 교차 결합되고,상기 퍼프 어레이는, 출력 로직 레벨을 결정하기 위한 평가 모드로 진입하기 전에, 상기 제1 인버터부와 상기 제2 인버터부에 챌린지 신호가 입력되어 상기 디지털 난수 생성 장치의 동작 특성이 재구성되도록 하며, 상기 챌린지 신호에 대한 응답 신호를 생성하는, 디지털 난수 생성 장치. |

| 16 | 제15항에 있어서,상기 퍼프 어레이는, 상기 디지털 난수 생성 장치가 리셋 모드로 동작하는 동안, 상기 제1 인버터부 및 상기 제2 인버터부로 전원이 인가되지 않도록 하고, 상기 디지털 난수 생성 장치가 상기 평가 모드로 진입하면, 상기 제1 인버터부 및 상기 제2 인버터부로 전원이 인가되도록 하는 제3 스위칭부를 더 포함하는, 디지털 난수 생성 장치. |

| 17 | 제15항에 있어서,상기 퍼프 어레이 내의 퍼프 셀에 대한 레이아웃은,상기 제1 인버터부를 구성하는 트랜지스터들 및 상기 제2 인버터부를 구성하는 트랜지스터들이 수평 방향 및 수직 방향에 따라 대칭적으로 배치된 것을 특징으로 하는, 디지털 난수 생성 장치. |

| 18 | 제15항에 있어서,상기 퍼프 어레이의 각 행(row)에 입력되어 상기 퍼프 어레이에 의해 생성되는 응답 신호를 출력하기 위한 워드라인(W/L: Word Line) 신호를 생성하는 행 디코더(Row Decorder); 및상기 행 디코더에 의해 생성된 워드라인 신호를 상기 퍼프 어레이로 드라이빙하는 워드라인 드라이버(W/L Driver)를 더 포함하는 것을 특징으로 하는 디지털 난수 생성 장치. |

| 19 | 제18항에 있어서,상기 제어기는, 입력되는 클록 신호를 기반으로 상기 행 디코더에 의해 생성된 워드라인 신호가 상기 퍼프 어레이로 입력되는 타이밍을 지연시키기 위한 지연 클록 신호를 생성하고,상기 워드라인 드라이버는, 상기 행 디코더에 의해 생성된 워드라인 신호를 상기 제어기에 의해 생성된 지연 클락 신호에 동기화하여 상기 퍼프 어레이로 입력하는 것을 특징으로 하는 디지털 난수 생성 장치. |