| 번호 | 청구항 |

|---|---|

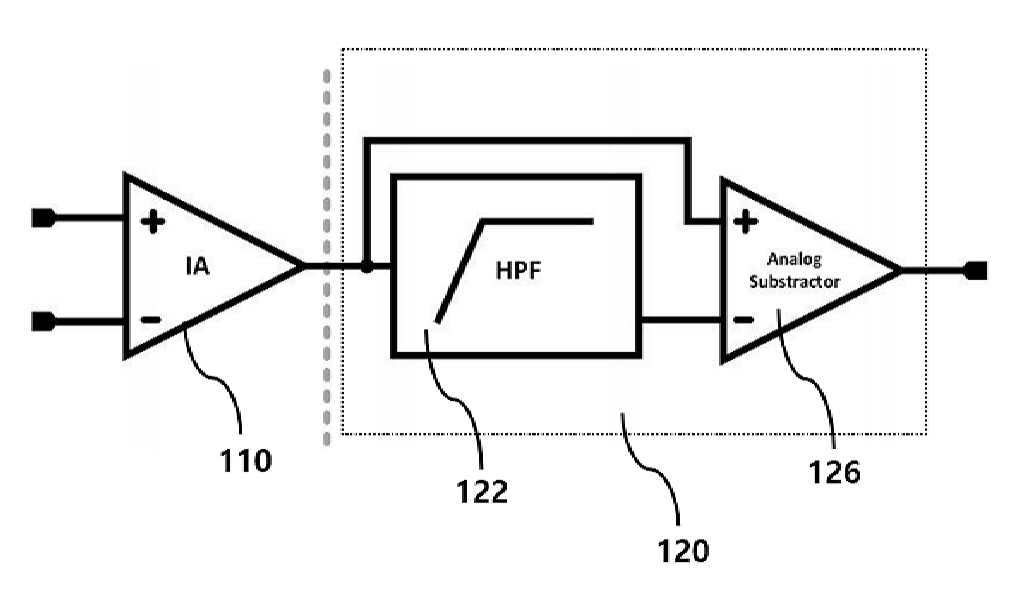

| 1 | 증폭기의 후단에 위치되는 동적 성능 개선 회로 장치에 있어서,상기 증폭기의 후단에 위치되며, 상기 증폭기를 통과한 아날로그 신호를 입력받은 후 하모닉 왜곡 주파수의 신호를 감쇄시켜 출력하는 하이 패스 필터; 및상기 하이 패스 필터 후단에 위치되며, 상기 증폭기를 통과한 아날로그 신호에서 상기 하이 패스 필터의 출력을 차감하여 예측 가능한 스퍼(spur)를 약화시키는 감산기를 포함하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 2 | 제1 항에 있어서,상기 하이 패스 필터는 상기 증폭기의 입력 신호에 대한 n차 하모닉 왜곡이 형성되는 주파수로 차단 주파수가 설정되되,상기 n은 3이상의 홀수인 것을 특징으로 하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 3 | 제1 항에 있어서,상기 증폭기는 단일 종단 증폭기 및 차동 증폭기 중 어느 하나인 것을 특징으로 하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 4 | 아날로그 증폭기; 및 상기 아날로그 증폭기의 후단에 위치되며, 상기 아날로그 증폭기를 통과한 아날로그 신호에서 하모닉 왜곡 주파수의 신호를 감쇄시키고, 상기 아날로그 증폭기를 통과한 아날로그 신호에서 상기 감쇄된 신호를 차감하여 출력하는 왜곡 개선 회로부를 포함하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 5 | 제4 항에 있어서,상기 왜곡 개선 회로부는, 상기 아날로그 증폭기를 통과한 아날로그 신호를 입력받은 후 하모닉 왜곡 주파수의 신호를 감쇄시켜 출력하는 하이 패스 필터; 및상기 하이 패스 필터 후단에 위치되며, 상기 아날로그 증폭기를 통과한 아날로그 신호에서 상기 하이 패스 필터의 출력을 차감하여 예측 가능한 스퍼(spur)를 약화시키는 감산기를 포함하는 것을 특징으로 하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 6 | 제4 항에 있어서,상기 하이 패스 필터는 상기 증폭기의 입력 신호에 대한 n차 하모닉 왜곡이 형성되는 주파수로 차단 주파수가 설정되되,상기 n은 3이상의 홀수인 것을 특징으로 하는 증폭기의 왜곡 제거 가능한 동적 성능 개선 회로 장치. |

| 7 | (a) 신호를 아날로그 증폭기에 적용하는 단계;(b) 상기 아날로그 증폭기를 통과한 아날로그 신호를 하이 패스 필터로 전달하여 하모닉 왜곡 주파수의 신호를 감쇄시켜 출력하는 단계; 및(c) 상기 아날로그 증폭기를 통과한 아날로그 신호를 감산기의 (+) 입력 단자로 전달하고 상기 하이 패스 필터의 출력을 상기 감산기의 (-) 입력 단자로 전달하여 상기 아날로그 증폭기를 통과한 아날로그 신호에서 상기 하이 패스 필터의 출력을 차감하여 예측 가능한 스퍼(spur)를 약화시키는 단계를 포함하는 증폭기의 왜곡 제거 가능한 동적 성능 향상 방법. |

| 8 | 제7 항에 있어서, 상기 (b) 단계 이전에,상기 하이 패스 필터의 차단 주파수를 설정하는 단계를 더 포함하되,상기 차단 주파수는 상기 아날로그 증폭기로 입력되는 상기 신호에 대한 n차 하모닉 왜곡 주파수로 설정되되, 상기 n은 3이상의 홀수인 것을 특징으로 하는 증폭기의 왜곡 제거 가능한 동적 성능 향상 방법. |