| 번호 | 청구항 |

|---|---|

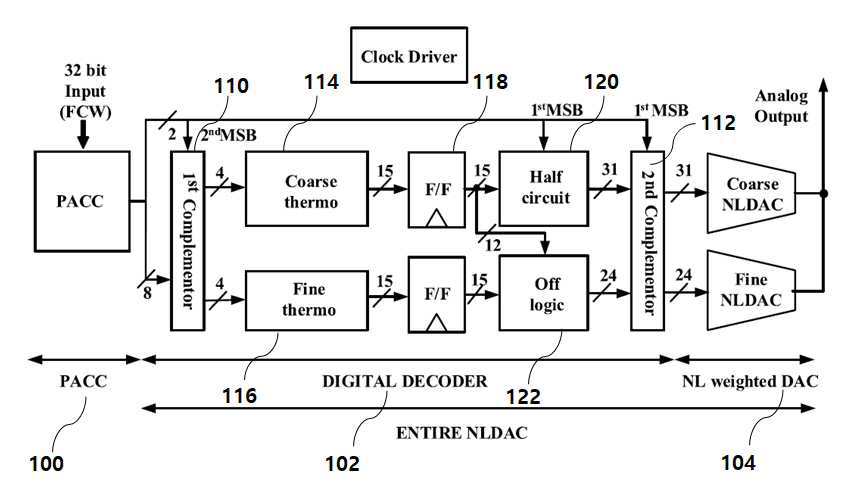

| 1 | 주파수 제어 워드를 누적하여 위상 정보를 생성하는 위상누적기;상기 위상누적기가 출력하는 위상 정보를 사인파의 진폭으로 변환하는 디지털 디코더; 및상기 디지털 디코더가 변환한 진폭을 아날로그 신호로 변환하여 출력하는 비선형 디지털 아날로그 변환기를 포함하되,디더링에 의한 주파수 오프셋을 보상하기 위해 상기 위상누적기는 의사난수 이진시퀀스가 더해지는 비트의 1/2 비중을 갖는 한 단계 하위 비트에서 1을 차감하는 주파수 오프셋 보상 회로를 포함하되, 상기 주파수 오프셋 보상 회로는 새로운 주파수 제어 워드가 입력될 때에만 동작하는 직접 디지털 주파수 합성기. |

| 2 | 삭제 |

| 3 | 제1항에 있어서, 상기 위상누적기는 상기 의사난수 이진시퀀스가 더해지는 경우 발생하는 오차가 상기 직접 디지털 주파수 합성기의 최소 주파수 조절 단위 이하가 되도록 하기 위해 아래의 수학식을 만족하도록 설정되는 직접 디지털 주파수 합성기. [수학식]여기서, 는 직접 디지털 주파수 합성기의 동작 주파수, L은 의사난수 이진시퀀스의 길이, N은 위상누적기의 입력 비트수, A는 의사난수 이진시퀀스가 더해지는 비트의 위치임 |

| 4 | 주파수 제어 워드를 누적하여 위상 정보를 생성하는 위상누적기;상기 위상누적기가 출력하는 위상 정보를 사인파의 진폭으로 변환하는 디지털 디코더; 및상기 디지털 디코더가 변환한 진폭을 아날로그 신호로 변환하여 출력하는 비선형 디지털 아날로그 변환기를 포함하되,상기 위상누적기는 상기 주파수 제어 워드의 A 비트에 의사난수 이진시퀀스를 더하는 디더링 회로를 포함하고, 디더링에 의한 주파수 오프셋을 보상하기 위해 상기 위상누적기는 상기 의사난수 이진시퀀스가 더해지는 비트의 1/2 비중을 갖는 한 단계 하위 비트에서 1을 차감하는 주파수 오프셋 보상 회로를 포함하고, 상기 주파수 오프셋 보상 회로는 새로운 주파수 제어 워드가 입력될 때에만 동작하는 직접 디지털 주파수 합성기. |