| 번호 | 청구항 |

|---|---|

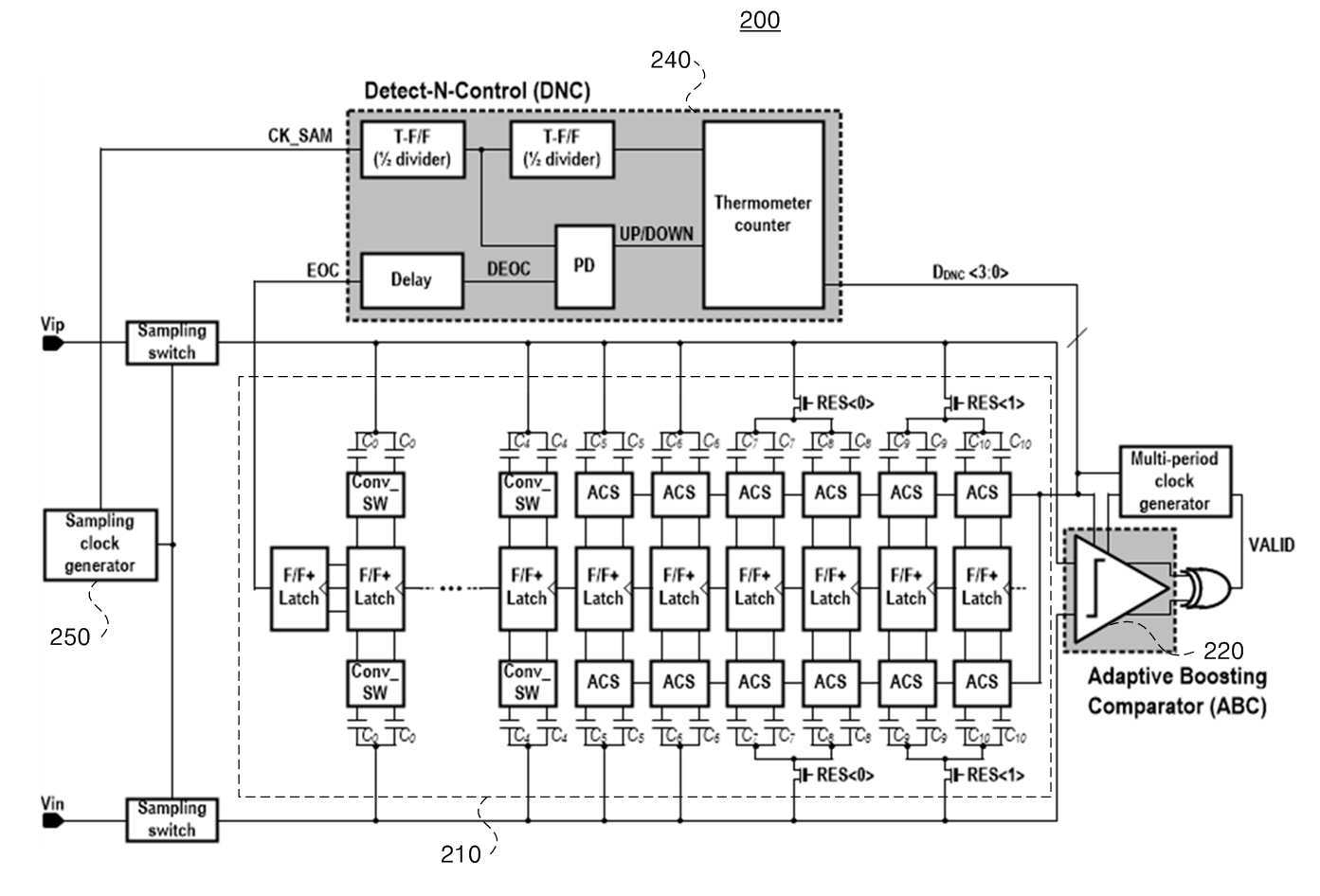

| 1 | 아날로그 디지털 컨버터에 있어서, 다수 개의 캐패시터를 포함하는 디지털 아날로그 변환부;상기 디지털 아날로그 변환부의 출력 신호와 미리 지정된 값을 비교하는 비교기; 상기 비교기의 출력 신호를 이용하여 아날로그 입력 전압을 n 비트의 디지털 신호로 변환하는 SAR 논리 회로; 및상기 비교기를 구동시키기 위한 전원 전압 및 접지 전압 중 적어도 일부의 전압을 제어하는 전압 제어부;를 포함하되, 상기 전압 제어부는, DEOC(Delayed End Of Conversion)를 이용하여 상기 적어도 일부의 전압을 제어하되, 상기 DEOC는 상기 다수 개의 캐패시터를 통해 아날로그 디지털 변환이 완료되었음을 알리는 EOC(End Of Conversion) 신호의 시간 지연된 값이며, 상기 전압 제어부는, 현재 샘플링 클럭에서의 상기 DEOC와 다음 번의 샘플링 클럭의 라이징 에지값을 비교하여 상기 적어도 일부의 전압을 제어하며, 상기 DEOC가 상기 다음 번의 샘플링 클럭의 라이징 에지값보다 빠르게 발생되는 경우, 상기 전압 제어부는 상기 전원 전압을 감소시키거나 상기 접지 전압을 상승시키도록 제어하고, 상기 DEOC가 상기 다음 번의 샘플링 클럭의 라이징 에지값보다 늦게 발생되는 경우, 상기 전압 제어부는 상기 전원 전압을 증가시키거나 상기 접지 전압을 하강시키도록 제어하는 것을 특징으로 하는 아날로그 디지털 컨버터. |

| 2 | 제1항에 있어서, 상기 디지털 아날로그 변환부는 다수 개의 스위치를 더 포함하고, 상기 전원 전압 및 상기 접지 전압은 상기 다수 개의 스위치를 구동하는데 더 사용되는 것을 특징으로 하는 아날로그 디지털 컨버터. |

| 3 | 제1항에 있어서, 상기 EOC는 상기 아날로그 디지털 컨버터의 변환 속도와 대응되는 것을 특징으로 하는 아날로그 디지털 컨버터. |

| 4 | 제1항에 있어서, 상기 아날로그 디지털 컨버터는 최상위 비트부터 최하위 비트까지 순차적으로 비트를 변환하는 SAR(Successive Approximation Register) 아날로그 디지털 컨버터이고, 상기 EOC는 상기 다수 개의 캐패시터에서 상기 최하위 비트가 결정되는 시점인 것을 특징으로 하는 아날로그 디지털 컨버터. |

| 5 | 삭제 |

| 6 | 삭제 |

| 7 | 아날로그 디지털 컨버터에 포함되는 전압 제어 장치에 있어서, 현재 샘플링 클럭에서의 EOC(End Of Conversion) 신호를 시간 지연하여 DEOC를 출력하는 시간 지연기;상기 DEOC와 다음 번 샘플링 클럭에서의 라이징 에지값을 비교하는 위상 검출기; 및 상기 위상 검출기의 출력 신호를 이용하여 상기 아날로그 디지털 컨버터 내의 비교기를 구동시키기 위한 전원 전압 및 접지 전압 중 적어도 일부의 전압을 제어하는 제어 신호를 출력하는 제어 신호 생성부;를 포함하되, 상기 제어 신호 생성부는 상기 DEOC가 상기 다음 번의 샘플링 클럭의 라이징 에지값보다 빠르게 발생되는 경우, 상기 전원 전압을 감소시키거나 상기 접지 전압을 상승시키도록 하는 제어 신호를 출력하고, 상기 DEOC가 상기 다음 번의 샘플링 클럭의 라이징 에지값보다 늦게 발생되는 경우, 상기 전원 전압을 증가시키거나 상기 접지 전압을 하강시키도록 하는 제어 신호를 출력하는 것을 특징으로 하는 전압 제어 장치. |