| 번호 | 청구항 |

|---|---|

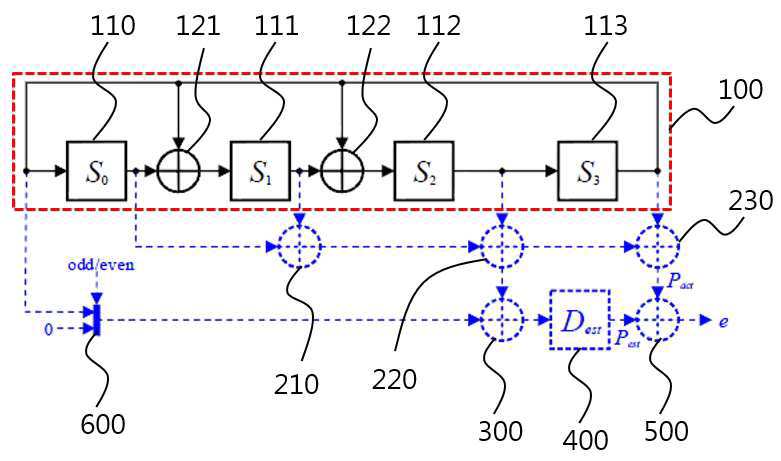

| 1 | 소정수의 비트가 저장되는 적어도 하나의 시프트 레지스터를 포함하고, 선형 피드백을 이용하여 순서화된 상기 비트가 클록의 주기에 따라 시프트 되는 LFSR;상기 시프트 레지스터에 저장된 각 신호를 이용하여 순차적으로 패리티 비트를 생성하는 패리티 생성부;상기 LFSR의 출력 이전 상태에서 생성되는 패리티 비트와, 상기 LFSR의 다항식 패리티에 따라 LFSR로부터 출력되는 피드백 신호 또는 0을 이용하여 추정 패리티 비트를 생성하는 패리티 추정부;상기 패리티 추정부에서 생성되는 추정 패리티 비트를 저장하는 패리티 저장부; 및상기 LFSR로부터 출력되는 신호를 이용하여 생성되는 실제 패리티 비트와, 상기 추정 패리티 비트를 비교하여 LFSR의 오류를 검출하는 비교부를 포함하고,상기 추정 패리티 비트는 i번째 클록 사이클에서 (n-1)번째 시프트 레지스터에 대한 패리티 함수와 피드백 신호에 대한 패리티 함수의 합을 이용하여 산출되는 것을 특징으로 하는 면적-효율적인 내결함성을 갖는 선형 피드백 시프트 레지스터. |

| 2 | 제1항에 있어서,상기 추정 패리티 비트는 아래의 [수학식 1]을 이용하여 산출되는 것을 특징으로 하는 면적-효율적인 내결함성을 갖는 선형 피드백 시프트 레지스터.[수학식 1]여기에서, N은 LFSR에서 시프트 레지스터(Shift register)의 수이고, n은 다항식의 수이며, i는 클록 사이클 인덱스를 나타낸다. 이때, 이다.또한, 는 추정 패리티 비트이고, F[i]는 피드백 신호이며, 은 발생기 다항식 내의 계수를 나타낸다. 또한, P()는 패리티 함수를 나타내고, 는 i번째 클록 사이클에서 (n-1)번째 시프트 레지스터를 나타낸다. |

| 3 | 제1항에 있어서,상기 실제 패리티 비트는 아래의 [수학식 2]를 이용하여 산출되는 것을 특징으로 하는 면적-효율적인 내결함성을 갖는 선형 피드백 시프트 레지스터.[수학식 2]여기에서, 는 실제 패리티 비트를 나타낸다. 또한, P()는 패리티 함수를 나타내고, 은 (i+1) 번째 클록 사이클에서 n 번째 시프트 레지스터를 나타낸다. |

| 4 | 제2항에 있어서,상기 LFSR의 다항식 패리티에 따라 LFSR로부터 피드백 되는 피드백 신호 또는 0을 선택적으로 출력하여 상기 패리티 추정부에 전송하는 피드백 선택부를 더 포함하는 면적-효율적인 내결함성을 갖는 선형 피드백 시프트 레지스터. |

| 5 | 패리티 생성부가 LFSR의 각 시프트 레지스터에 저장된 신호를 이용하여 순차적으로 패리티 비트를 생성하는 단계(S10);패리티 추정부가 상기 LFSR의 출력 이전 상태((N-1)번째 시프트 레지스터의 i번째 클록 사이클)에서 생성되는 패리티 비트와, 상기 LFSR의 다항식 패리티에 따라 LFSR로부터 출력되는 피드백 신호 또는 0을 이용하여 추정 패리티 비트를 생성하는 단계(S20);상기 추정 패리티 비트를 저장하는 단계(S30);클록의 주기에 따라 (i+1) 번째 클록 사이클에서 상기 LFSR의 각 시프트 레지스터에 저장된 신호가 순차적으로 시프트되는 단계(S40);상기 LFSR의 출력 상태(N번째 시프트 레지스터의 (i+1)번째 클록 사이클)에서 생성되는 신호를 이용하여 실제 패리티 비트를 생성하는 단계(S50); 및비교부가 상기 추정 패리티 비트와 실세 패리티 비트를 비교하여 LFSR의 오류를 검출하는 단계(S60)를 포함하고,상기 추정 패리티 비트는 i번째 클록 사이클에서 (n-1)번째 시프트 레지스터에 대한 패리티 함수와 피드백 신호에 대한 패리티 함수의 합을 이용하여 산출되는 것을 특징으로 하는 FT-LFSR을 이용한 오류 검출 방법. |