| 번호 | 청구항 |

|---|---|

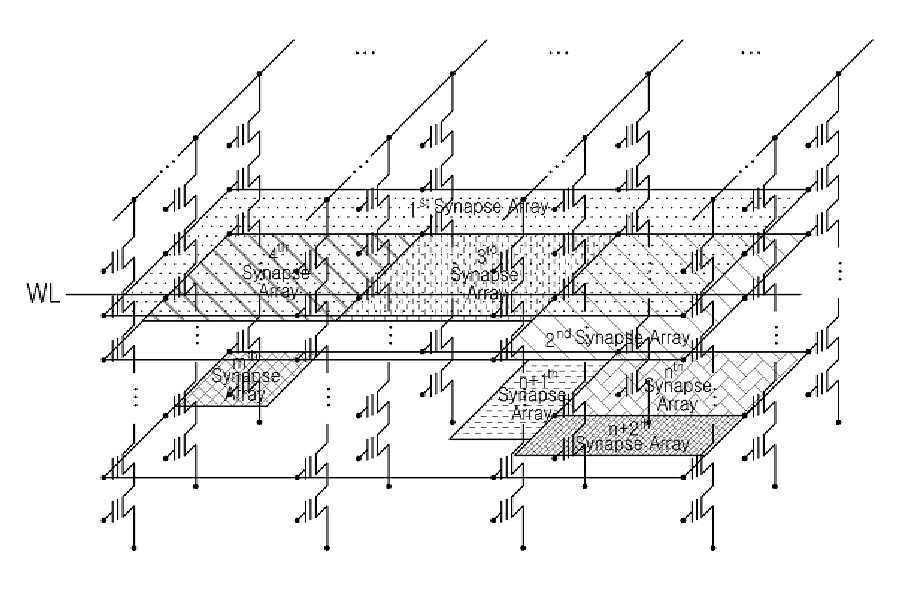

| 1 | 제1 시냅스 레이어 및 제2 시냅스 레이어를 포함하는 시냅스 소자 매핑 방법에 있어서, 상기 제1 시냅스 레이어 및 제2 상기 시냅스 레이어 각각은 워드라인, 스트링 선택라인 및 비트라인을 각각 포함하고, 워드라인(Word Line; WL)을 통한 벡터, 행렬곱 연산을 위해 해당하는 제1 시냅스 레이어를 활성화하기 위해 리드 전압(Vread)을 상응하는 워드라인(Word Line; WL) 층에 인가하고, 나머지 워드라인에는 패스 전압(Vpass)를 인가하는 단계; 제1 스트링 선택 라인(String Selection Lines; SSLs)을 통해 해당하는 제1 시냅스 레이어의 크기에 맞는 제1 스트링 선택 라인 입력과 제1 비트 라인(Bitlines; BLs) 출력만 활성화시키는 단계; 및 제1 비트 라인을 통해 같은 워드라인 층을 활성화 시킨 상태에서 상기 출력된 제1 비트 라인 출력을 제2 시냅스 레이어의 크기에 맞는 제2 스트링 선택 라인 입력에 인가하고 제2 시냅스 레이어에 해당하는 제2 비트 라인 출력을 활성화시키는 단계를 포함하고, 상기 제1 비트 라인을 통해 같은 워드라인 층을 활성화 시킨 상태에서 상기 출력된 제1 비트 라인 출력을 제2 시냅스 레이어의 크기에 맞는 제2 스트링 선택 라인 입력에 인가하고 제2 시냅스 레이어에 해당하는 제2 비트 라인 출력을 활성화시키는 단계는, 상기 제2 시냅스 레이어의 행렬곱 연산을 진행하고, 복수의 시냅스 레이어 각각의 크기에 따라 유동적으로 하나의 워드라인 층에 복수의 시냅스 레이어를 매핑하여, 복수의 시냅스 레이어 각각에 해당하는 스트링 선택 라인 및 비트 라인을 순차적으로 활성화시킴으로써 인공신경망의 추론과정을 구현하여 셀 낭비를 감소시키는 시냅스 소자를 매핑 방법. |

| 2 | 제1항에 있어서, 상기 제1 스트링 선택 라인(String Selection Lines; SSLs)을 통해 해당하는 제1 시냅스 레이어의 크기에 맞는 제1 스트링 선택 라인 입력과 제1 비트 라인 출력만 활성화시키는 단계는, 상기 제1 스트링 선택 라인 입력에 따른 상기 제1 비트 라인 출력의 전류를 읽음으로써 활성화된 셀만을 포함하는 상기 제1 시냅스 레이어의 행렬곱 연산을 진행하는시냅스 소자를 매핑 방법. |

| 3 | 삭제 |

| 4 | 제1 시냅스 레이어 및 제2 시냅스 레이어를 포함하는 시냅스 소자에 있어서, 상기 제1 시냅스 레이어 및 상기 제2 시냅스 레이어 각각은, 벡터, 행렬곱 연산을 위해 해당하는 제1 시냅스 레이어를 활성화하기 위한 해당 워드라인(Word Line; WL) 층에는 리드 전압(Vread)이 인가되고, 나머지 워드라인에는 패스 전압(Vpass)이 인가되는 워드라인; 해당하는 제1 시냅스 레이어의 크기에 맞춰 활성화되는 제1 스트링 선택 라인(String Selection Lines; SSLs); 및해당하는 제1 시냅스 레이어의 크기에 맞춰 활성화되는 제1 비트 라인(Bitlines; BLs)을 포함하고, 같은 워드라인 층을 활성화 시킨 상태에서 상기 활성화된 제1 비트 라인의 출력을 제2 시냅스 레이어의 크기에 맞는 제2 스트링 선택 라인 입력에 인가하고 제2 시냅스 레이어에 해당하는 제2 비트 라인 출력을 활성화시키고, 상기 제2 시냅스 레이어의 행렬곱 연산을 진행하고, 복수의 시냅스 레이어 각각의 크기에 따라 유동적으로 하나의 워드라인 층에 복수의 시냅스 레이어를 매핑하여, 복수의 시냅스 레이어 각각에 해당하는 스트링 선택 라인 및 비트 라인을 순차적으로 활성화시킴으로써 인공신경망의 추론과정을 구현하여 셀 낭비를 감소시키는시냅스 소자. |

| 5 | 제4항에 있어서, 상기 제1 스트링 선택 라인 입력에 따른 상기 제1 비트 라인 출력의 전류를 읽음으로써 활성화된 셀만을 포함하는 상기 제1 시냅스 레이어의 행렬곱 연산을 진행하는시냅스 소자. |

| 6 | 삭제 |