| 번호 | 청구항 |

|---|---|

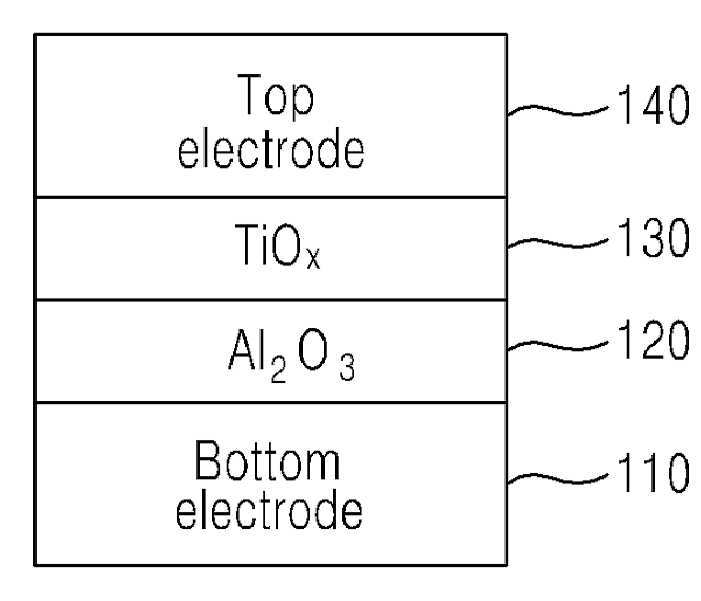

| 1 | 터널링 기반 메모리 소자에 있어서, 하부 전극(Bottom electrode) 상에 전도층이 적층되고,상기 전도층 상에 산화물층이 적층되고, 상기 산화물층 상에 상부 전극(Top electrode)이 적층되며,멤리스터 크로스바 어레이의 구조를 갖고, 하드웨어의 예측할 수 없는 물리적 복제불가 함수(Physically Unclonable Function; PUF)를 메모리 반도체 어레이로 구성할 때 상기 전도층과 상기 산화물층 간의 터널링 메커니즘으로 인한 외부 환경 변수인 온도에 독립적인 전류-전압 특성을 가지며,상기 터널링 기반 메모리 소자의 물리적 복제 방지를 위해, 터널링 기반의 멤리스터 크로스바 어레이의 구조를 갖는 메모리 소자를 이용하여 물리적 복제불가 함수를 구성하기 위해 챌린지를 인가하고, 상기 인가된 챌린지를 이용하여 전압-전류 특성에 따른 리스폰스 추출하며, 미리 등록된 리스폰스와 상기 추출된 리스폰스와의 확인을 통한 인증을 수행하고, 챌린지-리스폰스 페어를 형성하기 위해 상기 멤리스터 크로스바 어레이의 각 워드라인(wordline)에 챌린지의 디지털 신호에 해당하는 전압을 인가하여 멤리스터 소자의 전도도와 벡터 및 행렬곱 연산을 통해 각 비트라인(bitline)에 전류가 흐르도록 하고, 전체 비트라인에서 선택된 절반 비트라인에 흐르는 전류를 더하고 선택되지 않은 절반의 비트라인에 흐르는 전류를 더하여 각각 서로 다른 레지스터에 저장하는터널링 기반 메모리 소자. |

| 2 | 제1항에 있어서,상기 전도층의 두께를 조절하여 터널링 기반의 전도 메커니즘으로 동작하는 스택 구조를 갖는터널링 기반 메모리 소자. |

| 3 | 제1항에 있어서, 상기 터널링 기반의 멤리스터 크로스바 어레이의 구조를 갖는 메모리 소자는 온도에 독립적인 전류-전압 특성을 가짐으로써 물리적 복제불가 함수를 위한 보안인증과정에서의 에러가 발생하지 않도록 하는 BER(Bit-Error Rate)을 감소시키는 터널링 기반 메모리 소자. |

| 4 | 터널링 기반의 멤리스터 크로스바 어레이의 구조를 갖는 메모리 소자를 이용하여 물리적 복제불가 함수를 구성하기 위해 챌린지를 인가하는 단계; 상기 인가된 챌린지를 이용하여 전압-전류 특성에 따른 리스폰스 추출 단계; 및미리 등록된 리스폰스와 상기 추출된 리스폰스와의 확인을 통한 인증 단계를 포함하고, 상기 터널링 기반의 멤리스터 크로스바 어레이의 구조를 갖는 메모리 소자를 이용하여 물리적 복제불가 함수를 구성하기 위해 챌린지를 인가하는 단계는, 챌린지-리스폰스 페어를 형성하기 위해 상기 멤리스터 크로스바 어레이의 각 워드라인(wordline)에 챌린지의 디지털 신호에 해당하는 전압을 인가하여 멤리스터 소자의 전도도와 벡터 및 행렬곱 연산을 통해 각 비트라인(bitline)에 전류가 흐르도록 하고, 전체 비트라인에서 선택된 절반 비트라인에 흐르는 전류를 더하고 선택되지 않은 절반의 비트라인에 흐르는 전류를 더하여 각각 서로 다른 레지스터에 저장하는물리적 복제 방지 방법. |

| 5 | 제4항에 있어서, 상기 터널링 기반의 멤리스터 크로스바 어레이의 구조를 갖는 메모리 소자는 멤리스터 크로스바 어레이의 구조를 갖고, 하드웨어의 예측할 수 없는 물리적 복제불가 함수(Physically Unclonable Function; PUF)를 메모리 반도체 어레이로 구성할 때 터널링 메커니즘으로 인한 외부 환경 변수인 온도에 독립적인 전류-전압 특성을 가짐으로써 물리적 복제불가 함수를 위한 보안인증과정에서의 에러가 발생하지 않도록 하는 BER(Bit-Error Rate)을 감소시키는 물리적 복제 방지 방법. |

| 6 | 삭제 |

| 7 | 제4항에 있어서, 상기 상기 인가된 챌린지를 이용하여 전압-전류 특성에 따른 리스폰스 추출 단계는, 상기 선택되지 않은 워드라인과 비트라인은 플로팅(floating) 또는 그라운드(ground)에 연결되고, 선택되지 않은 절반의 비트라인에 흐르는 전류를 더할 경우 선택된 나머지 비트라인들이 비트라인 또는 그라운드에 연결되며, 서로 다른 레지스터에 저장된 전류들은 전압으로 환산되어 비교기를 통해 대소 비교를 판단 후 0 또는 1의 1-bit 리스폰스를 생성하는 물리적 복제 방지 방법. |

| 8 | 제4항에 있어서, 상기 미리 등록된 리스폰스와 상기 추출된 리스폰스와의 확인을 통한 인증 단계는, 메모리 반도체 소자의 구동 원리에 따라 전압-전류 특성이 결정되고, 제조 상의 공정 편차 및 소자간 편차에 의해 같은 전압이 인가되더라도 다른 양의 전류가 흐르는 특징을 고유의 리스폰스로 활용하여 보안 기능을 구현하는 물리적 복제 방지 방법. |