| 번호 | 청구항 |

|---|---|

| 7 | 제 6 항에 있어서, 상기 컨트롤러는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 쉬프트 횟수를 산출하고, 상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 입력 횟수를 산출하며, 상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 출력 횟수를 산출하는, 메모리 장치. |

| 1 | 메모리 장치에 포함된 컨트롤러가 수행하는 방법으로서,심층 신경망에 포함되는 컨볼루션 레이어를 연산하도록 마련되는 PIM 어레이의 크기, 상기 컨볼루션 레이어에 입력되는 입력 데이터의 크기 및 상기 입력 데이터를 필터링하는 커널의 크기를 획득하는 단계; 및상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 컨볼루션 레이어에 대한 상기 PIM 어레이의 사이클 횟수가 최소화되도록 병렬 윈도우의 크기를 결정하는 단계;를 포함하되,상기 병렬 윈도우를 결정하는 단계는,입력 데이터에 대한 상기 병렬 윈도우의 쉬프트 횟수, 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로의 입력 횟수 및 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로부터의 출력 횟수 중 적어도 하나에 기초하여 상기 사이클 횟수를 산출하는, 메모리 장치의 제어방법. |

| 2 | 제 1 항에 있어서, 상기 병렬 윈도우를 결정하는 단계는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 쉬프트(Shift) 횟수를 산출하는 단계;상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 입력 횟수를 산출하는 단계; 및상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 출력 횟수를 산출하는 단계; 를 포함하는, 메모리 장치의 제어방법. |

| 3 | 제 2 항에 있어서, 상기 쉬프트 횟수를 산출하는 단계는,상기 입력 데이터의 크기 및 상기 커널의 크기 중 적어도 하나에 기초하여 상기 쉬프트 횟수를 산출하는, 메모리 장치의 제어방법. |

| 4 | 제 2 항에 있어서, 상기 입력 횟수를 산출하는 단계는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 입력 데이터에 따른 입력 채널의 개수 중 적어도 하나에 기초하여 상기 입력 횟수를 산출하는, 메모리 장치의 제어방법. |

| 5 | 제 2 항에 있어서, 상기 출력 횟수를 산출하는 단계는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기, 커널의 크기 및 상기 커널에 따른 출력 채널의 개수 중 적어도 하나에 기초하여 상기 출력 횟수를 산출하는, 메모리 장치의 제어방법. |

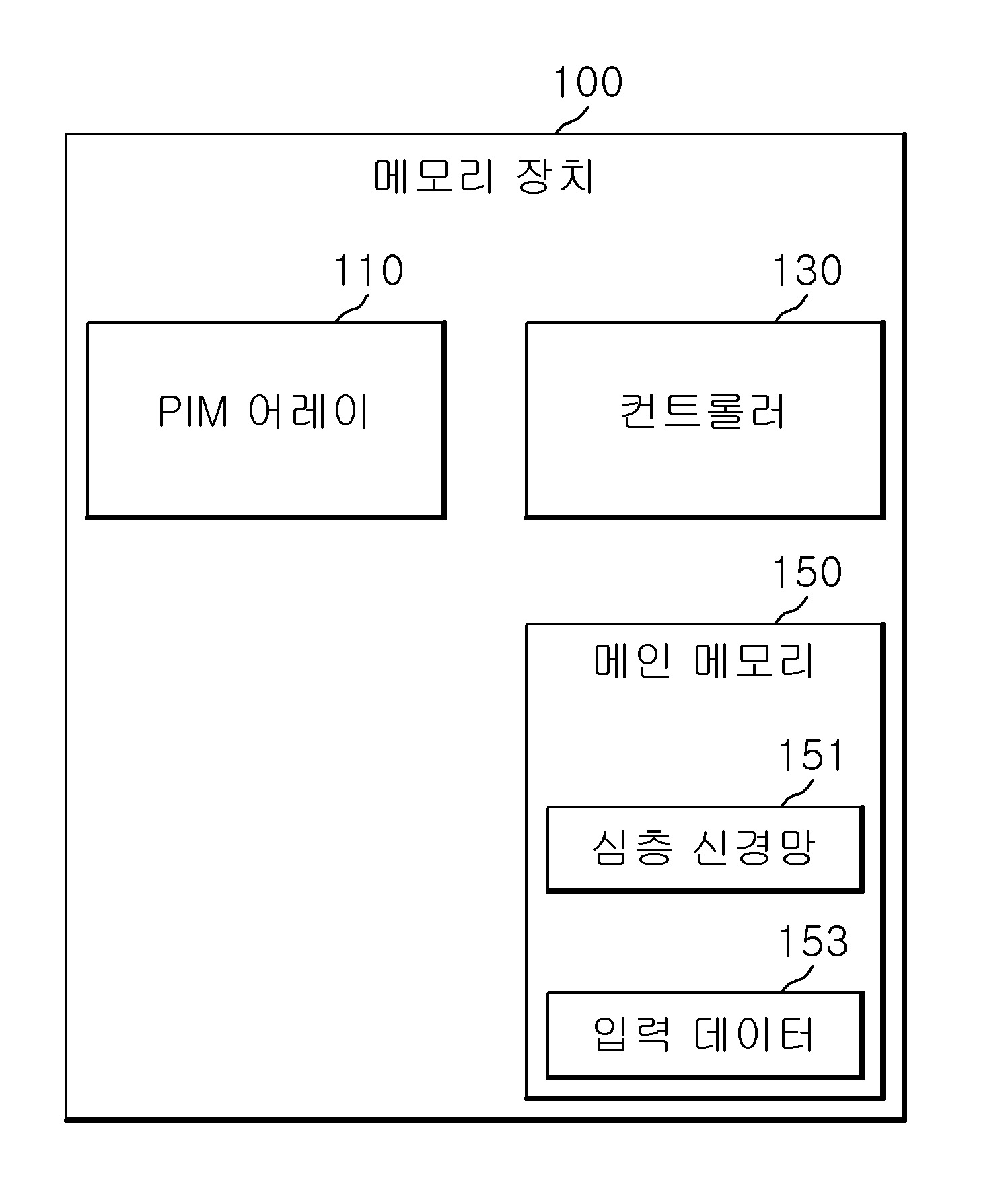

| 6 | 심층 신경망에 포함되는 컨볼루션 레이어를 연산하도록 마련되는 PIM 어레이; 및상기 PIM 어레이의 크기, 상기 컨볼루션 레이어에 입력되는 입력 데이터의 크기 및 상기 입력 데이터를 필터링하는 커널의 크기를 획득하고, 상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 컨볼루션 레이어에 대한 상기 PIM 어레이의 사이클 횟수가 최소화되도록 병렬 윈도우의 크기를 결정하는 컨트롤러;를 포함하되, 상기 컨트롤러는,입력 데이터에 대한 상기 병렬 윈도우의 쉬프트 횟수, 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로의 입력 횟수 및 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로부터의 출력 횟수 중 적어도 하나에 기초하여 상기 사이클 횟수를 산출하는, 메모리 장치. |

| 8 | 제 7 항에 있어서, 상기 컨트롤러는,상기 입력 데이터의 크기 및 상기 커널의 크기 중 적어도 하나에 기초하여 상기 쉬프트 횟수를 산출하는, 메모리 장치. |

| 9 | 제 7 항에 있어서, 상기 컨트롤러는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 입력 데이터에 따른 입력 채널의 개수 중 적어도 하나에 기초하여 상기 입력 횟수를 산출하는, 메모리 장치. |

| 10 | 제 7 항에 있어서, 상기 컨트롤러는,상기 PIM 어레이의 크기, 상기 입력 데이터의 크기, 커널의 크기 및 상기 커널에 따른 출력 채널의 개수 중 적어도 하나에 기초하여 상기 출력 횟수를 산출하는, 메모리 장치. |

| 11 | 컴퓨터 프로그램을 저장하고 있는 컴퓨터 판독 가능 기록매체로서,상기 컴퓨터 프로그램은, 프로세서에 의해 실행되면,심층 신경망에 포함되는 컨볼루션 레이어를 연산하도록 마련되는 PIM 어레이의 크기, 상기 컨볼루션 레이어에 입력되는 입력 데이터의 크기 및 상기 입력 데이터를 필터링하는 커널의 크기를 획득하는 단계; 및상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 컨볼루션 레이어에 대한 상기 PIM 어레이의 사이클 횟수가 최소화되도록 병렬 윈도우의 크기를 결정하는 단계;를 포함하는 방법을 상기 프로세서가 수행하도록 하기 위한 명령어를 포함하되,상기 병렬 윈도우를 결정하는 단계는,입력 데이터에 대한 상기 병렬 윈도우의 쉬프트 횟수, 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로의 입력 횟수 및 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로부터의 출력 횟수 중 적어도 하나에 기초하여 상기 사이클 횟수를 산출하는, 컴퓨터 판독 가능한 기록매체. |

| 12 | 컴퓨터 판독 가능한 기록매체에 저장되어 있는 컴퓨터 프로그램으로서,상기 컴퓨터 프로그램은, 프로세서에 의해 실행되면,심층 신경망에 포함되는 컨볼루션 레이어를 연산하도록 마련되는 PIM 어레이의 크기, 상기 컨볼루션 레이어에 입력되는 입력 데이터의 크기 및 상기 입력 데이터를 필터링하는 커널의 크기를 획득하는 단계; 및상기 PIM 어레이의 크기, 상기 입력 데이터의 크기 및 상기 커널의 크기에 기초하여 상기 컨볼루션 레이어에 대한 상기 PIM 어레이의 사이클 횟수가 최소화되도록 병렬 윈도우의 크기를 결정하는 단계;를 포함하는 방법을 상기 프로세서가 수행하도록 하기 위한 명령어를 포함하되,상기 병렬 윈도우를 결정하는 단계는,입력 데이터에 대한 상기 병렬 윈도우의 쉬프트 횟수, 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로의 입력 횟수 및 상기 병렬 윈도우의 크기에 따른 상기 PIM 어레이로부터의 출력 횟수 중 적어도 하나에 기초하여 상기 사이클 횟수를 산출하는, 컴퓨터 프로그램. |