| 번호 | 청구항 |

|---|---|

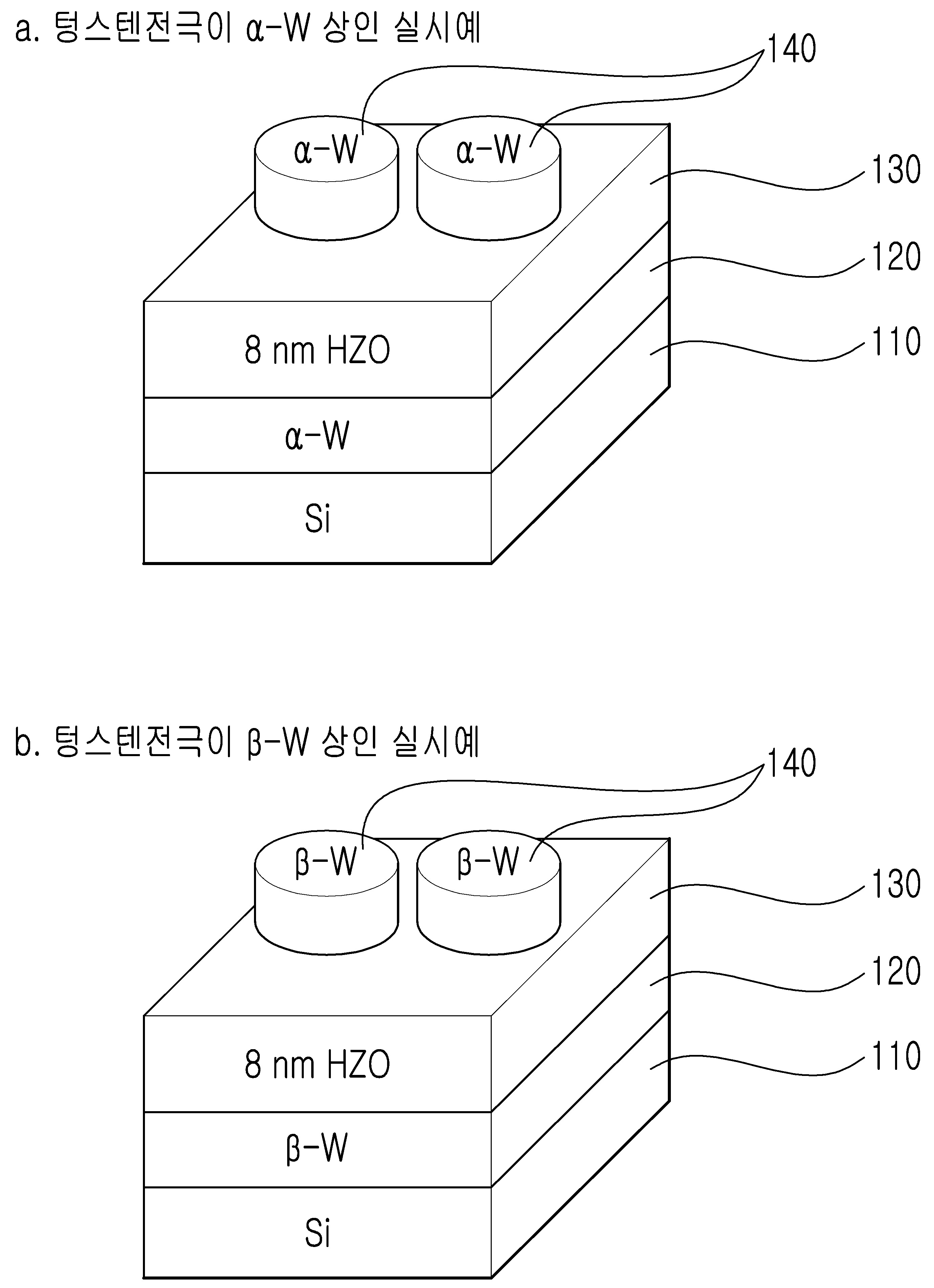

| 1 | 실리콘웨이퍼;상기 실리콘웨이퍼 위에 스퍼터링 기법으로 증착된 제1 텅스텐전극;상기 제1 텅스텐전극 위에 원자층증착법으로 증착된 강유전체층; 및상기 강유전체층 위에 스퍼터링 기법으로 증착된 제2 텅스텐전극;을 포함하고,상기 제1 및 제2 텅스텐 전극은 α-W 또는 β-W 상인 저전력 금속-강유전체-금속 커패시터. |

| 2 | 청구항 1에 있어서,상기 제1 및 제2 텅스텐전극의 증착 두께는 40 |

| 3 | 청구항 1에 있어서,상기 강유전체층의 성분은 Hf1-xZrxO2이고, 여기서 x의 값은 0보다 크고, 1보다 작은 값인 것을 특징으로 하는 저전력 금속-강유전체-금속 커패시터. |

| 4 | 실리콘웨이퍼 위에 스퍼터링 기법으로 제1 텅스텐전극을 증착하는 단계;상기 제1 텅스텐전극 위에 원자층증착법으로 강유전체층을 증착하는 단계;상기 강유전체층 위에 스퍼터링 기법으로 제2 텅스텐전극을 증착하는 단계; 및질소(N2) 분위기에서 450 |

| 5 | 청구항 4에 있어서,상기 제1 및 제2 텅스텐전극을 증착하는 단계에서상기 스퍼터링 기법은 DC 스퍼터링이고,상기 α-W 상을 증착하는 경우에는 플라즈마 파워 140 |

| 6 | 청구항 4에 있어서,상기 제1 및 제2 텅스텐전극을 증착하는 단계에서상기 스퍼터링 기법은 DC 스퍼터링이고,상기 β-W 상을 증착하는 경우에는 플라즈마 파워 140 |

| 7 | 청구항 4에 있어서,상기 강유전체층을 증착하는 단계에서상기 강유전체층의 성분은 Hf1-xZrxO2 이고,산화하프늄의 전구체는 [(CH3)(C2H5)N]4Hf(TEMA-Hf), 산화지르코늄의 전구체는 [(CH3)(C2H5)N]4Zr(TEMA-Zr)이 사용되며,상기 실리콘웨이퍼의 온도는 270~290oC 에서 원자층증착법으로 상기 강유전체층이 증착되는 것을 특징으로 하는 저전력 금속-강유전체-금속 커패시터 제조방법. |

| 8 | 청구항 4에 있어서,상기 제1 및 제2 텅스텐전극의 증착 두께는 40 |