| 번호 | 청구항 |

|---|---|

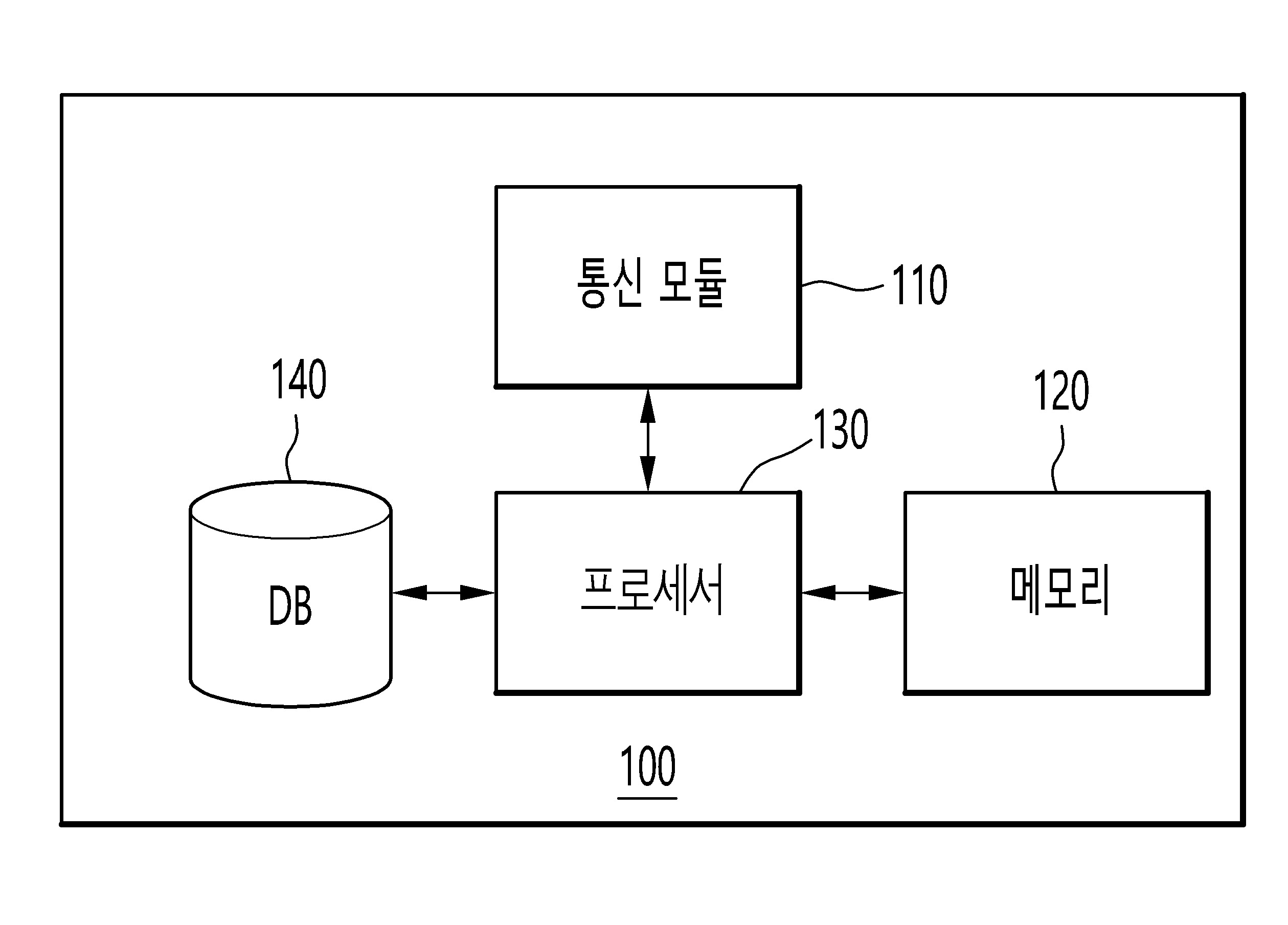

| 1 | DMA 컨트롤러 기반 메모리 접근 시간 모델링 장치에 있어서,메모리 접근 시간 모델링 프로그램이 저장된 메모리; 및상기 프로그램을 실행하는 프로세서를 포함하되,상기 프로그램은, 메인 메모리, 온칩 메모리 및 DMA(Direct Memory Access) 컨트롤러를 모사하는 가상 시스템에서 DMA 컨트롤러의 동작을 시뮬레이션하고, 분석 모델을 이용하여 상기 DMA 컨트롤러의 설정에 의해 상기 메인 메모리와 상기 온칩 메모리 간 데이터 전송에 소요되는 총 메모리 접근 시간을 예측하는 것인, 메모리 접근 시간 모델링 장치. |

| 2 | 제1항에 있어서,상기 프로그램은, 메인 메모리, 온칩 메모리, 출력 버퍼 및 DMA 컨트롤러를 모사하는 가상 NPU 시스템에서 DMA 컨트롤러의 동작을 시뮬레이션하되, 상기 DMA 컨트롤러의 동작은 상기 메인 메모리에서 상기 온칩 메모리로 데이터를 전송하거나, 상기 출력 버퍼에서 상기 메인 메모리로 데이터를 전송하도록 설정되는 것인, 메모리 접근 시간 모델링 장치. |

| 3 | 제1항에 있어서,상기 프로그램은, 상기 분석 모델을 이용하여, 수학식1에 따라 채널별 데이터 전송 시간과 DMA 설정 시간 중 더 큰 값을 선택하고, 상기 선택된 큰 값과 후처리 작업 시간을 합산하여 총 메모리 접근 시간을 계산하는 것인, 메모리 접근 시간 모델링 장치.003c#수학식1003e#여기서, TLchWise는 채널별 데이터 전송 시간이고, SL은 DMA 설정 시간이고, Cpostprocess는 데이터 전송 완료 후의 후처리 작업 시간이다. |

| 4 | 제3항에 있어서,상기 프로그램은, 수학식2에 의해, 상기 채널별 데이터 전송 시간을 계산하는 것인, 메모리 접근 시간 모델링 장치.003c#수학식2003e#여기서, TLchTrans는 순수 데이터 전송 시간이고, TLchOp는 데이터 전송 중 DMA 작업 시간이고, Cstart는 DMA 작업 시간 중 일정 지연 시간이다. |

| 5 | 제4항에 있어서,상기 프로그램은, 상기 수학식2에서 순수 데이터 전송시간을 계산하는 경우, N개 DMA 채널에 대하여 i번째 채널에서의 데이터 전송량을 근원지 메모리의 버스 폭과 목적지 메모리의 버스 폭으로 나누어 각각의 버스를 통해 전송되는 근원지 메모리 시간과 목적지 메모리 시간을 계산하고, 상기 근원지 메모리 시간과 상기 목적지 메모리 시간에 근원지 메모리의 지연 계수와 목적지 메모리의 지연 계수를 곱한 값을 합산하는 것인, 메모리 접근 시간 모델링 장치. |

| 6 | 제4항에 있어서,상기 프로그램은, 상기 수학식2에서 DMA 작업 시간을 계산하는 경우, N개 DMA 채널에 대하여 각 채널별 DMA 작업 시간과 각 채널별 DMA 작업 사이의 유휴 시간을 계산하고, 상기 각 채널별 DMA 작업 시간과 각 채널별 DMA 작업 사이의 유휴 시간을 합산하는 것인, 메모리 접근 시간 모델링 장치. |

| 7 | 제3항에 있어서,상기 프로그램은, 수학식 3에 의해, 상기 DMA 설정 시간을 계산하는 것인, 메모리 접근 시간 모델링 장치. 003c#수학식3003e#여기서, SLch는 각 채널의 설정 시간이고, Nreq는 요청된 DMA 채널의 수이고, SLpolling은 폴링을 위한 추가 설정 시간이다. |

| 8 | DMA 컨트롤러 기반 메모리 접근 시간 모델링 장치를 이용한 메모리 접근 시간 모델링 방법에 있어서,메인 메모리, 온칩 메모리 및 DMA(Direct Memory Access) 컨트롤러를 모사하는 가상 시스템에서 DMA 컨트롤러의 동작을 시뮬레이션하는 단계; 및분석 모델을 이용하여 상기 DMA 컨트롤러의 설정에 의해 상기 메인 메모리와 상기 온칩 메모리 간 데이터 전송에 소요되는 총 메모리 접근 시간을 예측하는 단계를 포함하는, 메모리 접근 시간 모델링 방법. |

| 9 | 제8항에 있어서,상기 시뮬레이션하는 단계는,메인 메모리, 온칩 메모리, 출력 버퍼 및 DMA 컨트롤러를 모사하는 가상 NPU 시스템에서 DMA 컨트롤러의 동작을 시뮬레이션하는 단계를 포함하되,상기 DMA 컨트롤러의 동작은 상기 메인 메모리에서 상기 온칩 메모리로 데이터를 전송하거나, 상기 출력 버퍼에서 상기 메인 메모리로 데이터를 전송하도록 설정되는 것인, 메모리 접근 시간 모델링 방법. |

| 10 | 제8항에 있어서,상기 총 메모리 접근 시간을 예측하는 단계는, 상기 분석 모델을 이용하여 수학식1에 따라 채널별 데이터 전송 시간과 DMA 설정 시간 중 더 큰 값을 선택하고, 상기 선택된 큰 값과 후처리 작업 시간을 합산하여 총 메모리 접근 시간을 계산하는 것인, 메모리 접근 시간 모델링 방법.003c#수학식1003e#여기서, TLchWise는 채널별 데이터 전송 시간이고, SL은 DMA 설정 시간이고, Cpostprocess는 데이터 전송 완료 후의 후처리 작업 시간이다. |

| 11 | 제10항에 있어서,상기 총 메모리 접근 시간을 예측하는 단계는, 수학식2에 의해, 상기 채널별 데이터 전송 시간을 계산하는 것인, 메모리 접근 시간 모델링 방법.003c#수학식2003e#여기서, TLchTrans는 순수 데이터 전송 시간이고, TLchOp는 데이터 전송 중 DMA 작업 시간이고, Cstart는 DMA 작업 시간 중 일정 지연 시간이다. |

| 12 | 제11항에 있어서,상기 총 메모리 접근 시간을 예측하는 단계는, 상기 수학식2에서 순수 데이터 전송시간을 계산하는 경우, N개 DMA 채널에 대하여 i번째 채널에서의 데이터 전송량을 근원지 메모리의 버스 폭과 목적지 메모리의 버스 폭으로 나누어 각각의 버스를 통해 전송되는 근원지 메모리 시간과 목적지 메모리 시간을 계산하는 단계 및 상기 근원지 메모리 시간과 상기 목적지 메모리 시간에 근원지 메모리의 지연 계수와 목적지 메모리의 지연 계수를 곱한 값을 합산하는 단계를 포함하는 것인, 메모리 접근 시간 모델링 방법. |

| 13 | 제11항에 있어서,상기 총 메모리 접근 시간을 예측하는 단계는, 상기 수학식2에서 DMA 작업 시간을 계산하는 경우, N개 DMA 채널에 대하여 각 채널별 DMA 작업 시간과 각 채널별 DMA 작업 사이의 유휴 시간을 계산하는 단계 및 상기 각 채널별 DMA 작업 시간과 각 채널별 DMA 작업 사이의 유휴 시간을 합산하는 단계를 포함하는 것인, 메모리 접근 시간 모델링 방법. |

| 14 | 제10항에 있어서,상기 총 메모리 접근 시간을 예측하는 단계는, 수학식 3에 의해, 상기 DMA 설정 시간을 계산하는 것인, 메모리 접근 시간 모델링 방법. 003c#수학식3003e#여기서, SLch는 각 채널의 설정 시간이고, Nreq는 요청된 DMA 채널의 수이고, SLpolling은 폴링을 위한 추가 설정 시간이다. |

| 15 | 제8항 내지 제14항 중 어느 한 항에 따른 메모리 접근 시간 모델링 방법을 수행하기 위한 컴퓨터 프로그램이 기록된 비일시적 컴퓨터 판독가능 기록매체. |