| 번호 | 청구항 |

|---|---|

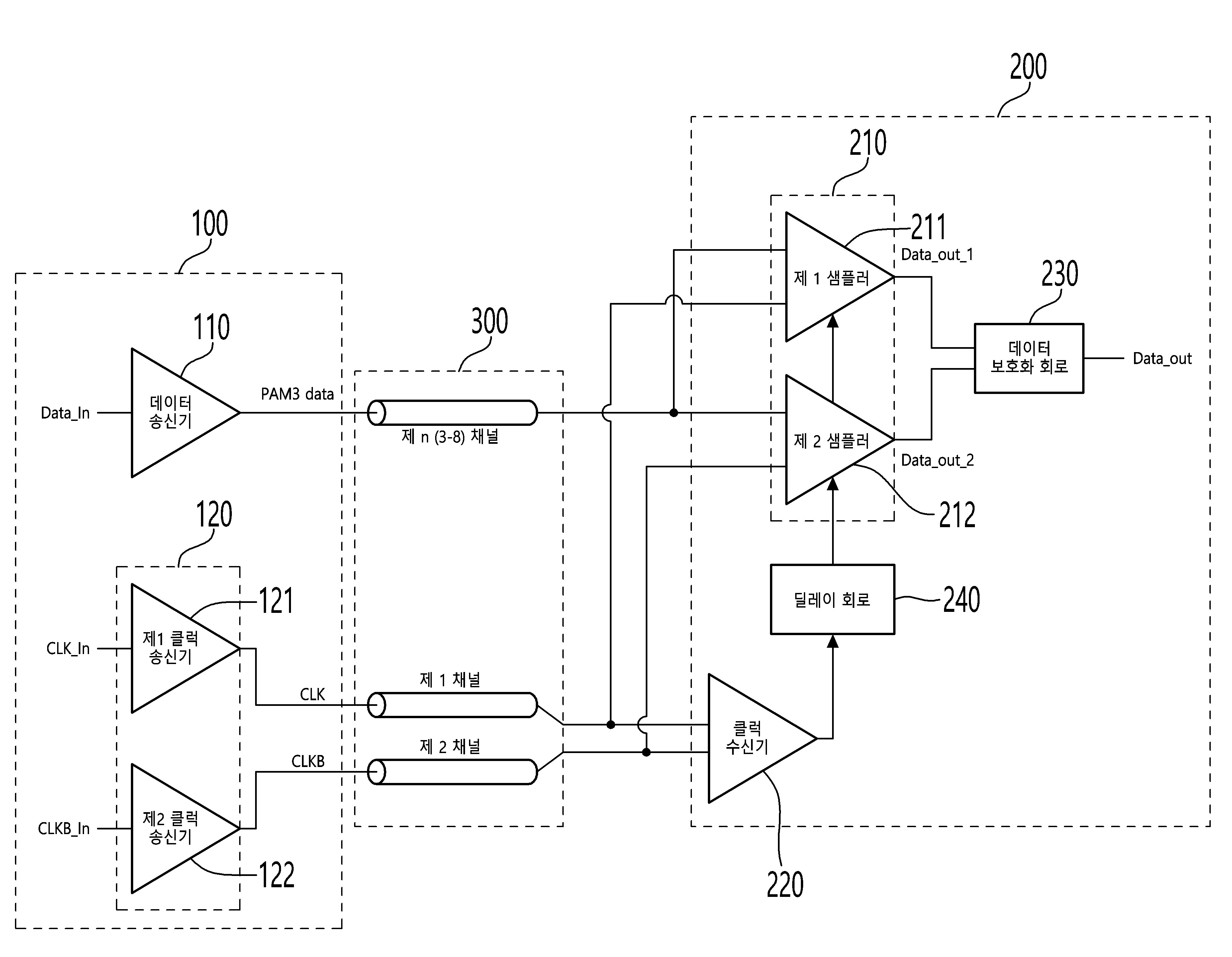

| 1 | 제 1 다이 및 제 2 다이를 포함하는 칩렛;상기 제1 다이에 포함되며, 단일 종단데이터를 PAM3 멀티레벨 신호로 변조하고, 생성된 PAM3 멀티레벨 신호 및 복수의 클럭 신호를 상기 제2 다이로 송신하는 송신칩; 및상기 제 2 다이에 포함되며, 상기 제1 다이로부터 수신된 상기 PAM3 멀티레벨 신호 및 클럭 신호를 차등 비교하여 단일 종단데이터를 생성하는 수신칩을 포함하되,상기 송신칩 및 수신칩은 복수의 채널로 연결되는 것이고,상기 송신칩은 상기 PAM3 멀티레벨 신호로 변조하는 데이터 송신기; 및상기 복수의 클럭 신호를 각각 송신하는 복수의 클럭 송신기를 포함하고, 상기 수신칩은,상기 복수의 클럭 송신기로부터 상기 복수의 클럭 신호를 수신하기 위한 클럭 수신기;상기 데이터 송신기와 상기 클럭 수신기로부터 각각 상기 PAM3 멀티레벨 신호와 복수의 클럭 신호를 수신하며, 수신된 상기 PAM3 멀티레벨 신호와 복수의 클럭 신호를 서로 차등비교하는 복수의 샘플러가 포함된 데이터 수신기; 및상기 복수의 샘플러를 통해 각각 차등비교된 신호를 복호화하는 데이터 복호화 회로를 포함하는 것이고, 상기 송신칩 및 수신칩을 연결하는 복수의 채널은, 제 1 클럭 송신기와 상기 클럭 수신기 사이의 신호를 전송하는 제 1 채널,제 2 클럭 송신기와 상기 클럭 수신기 사이의 신호를 전송하는 제 2 채널 및상기 데이터 송신기와 상기 데이터 수신기 사이의 신호를 전송하는 제 n 채널(상기 n은 3 이상 8 이하의 자연수)을 포함하고,상기 제 1 클럭 송신기와 제 2 클럭 송신기는 서로 차등된 클럭 신호를 각각 제 1 채널과 제 2 채널로 송신하되, 각각이 서로 다른 멀티레벨 진폭으로 변조된 클럭 신호를 송신하는 것인, 반도체 패키지. |

| 2 | 삭제 |

| 3 | 제 1 항에 있어서,상기 데이터 송신기는 2개의 단일 종단 데이터를 수신하여 3개의 멀티레벨로 진폭이 변조된 상기 PAM3 멀티레벨 신호를 생성하고,상기 3개의 멀티레벨은 각각 기설정된 기준 값을 갖는 3개의 전압레벨로 구성되는 것인, 반도체 패키지. |

| 4 | 삭제 |

| 5 | 제 1 항에 있어서,상기 복수의 클럭 송신기는 상기 채널의 감쇠를 상쇄하는 캐패시티브 등화기(capacitive equalizer) 및 상기 클럭 신호의 진폭을 변조하기 위한 기설정된 드라이버로 구성되는 것인, 반도체 패키지. |

| 6 | 삭제 |

| 7 | 제 1 항에 있어서,상기 클럭 수신기와 데이터 수신기 사이에는 딜레이 회로가 더 구비되며, 상기 딜레이 회로는 상기 복수의 샘플러의 신호를 비교하는 타이밍을 기설정된 방식에 따라 조절하는 것인, 반도체 패키지. |

| 8 | 제 1 항에 있어서,상기 데이터 복호화 회로는 상기 샘플러를 통해 상기 PAM3 멀티레벨 신호와 복수의 클럭 신호를 비교하는 과정에서, 상기 PAM3 멀티레벨 신호의 진폭과 클럭 신호의 진폭에 대한 높이 차이를 각각 데이터로 산출하여 복호화를 수행하는 것인, 반도체 패키지. |