| 번호 | 청구항 |

|---|---|

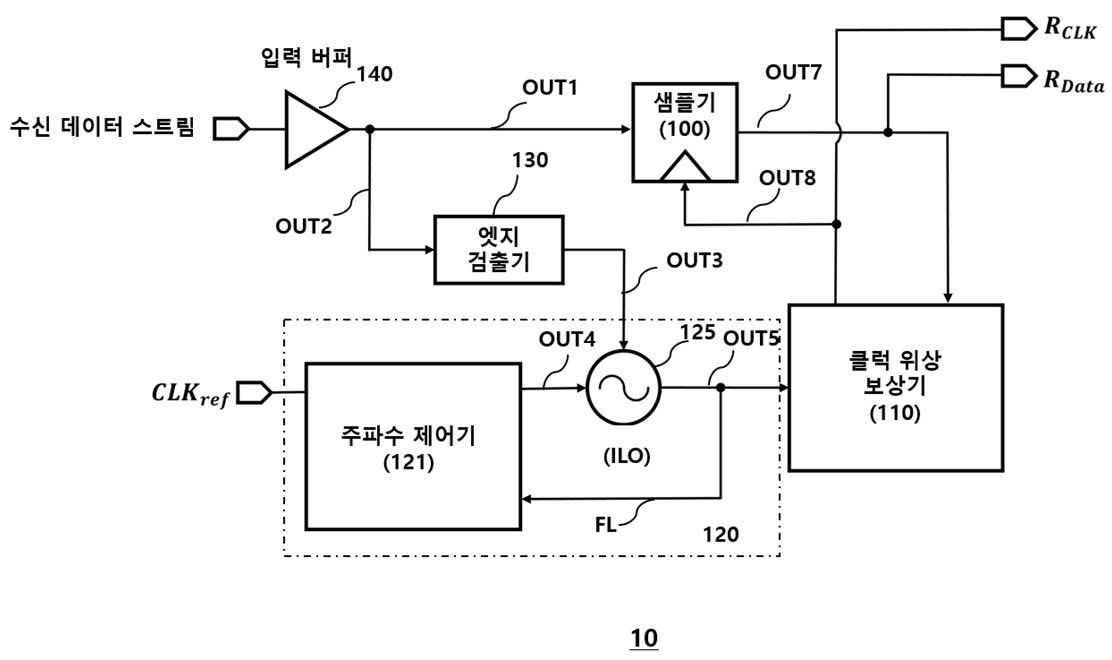

| 1 | 수신 데이터 스트림으로부터 클럭을 복원하고 상기 복원된 클럭을 이용하여 상기 수신 데이터 스트림을 샘플링하는 클럭 및 데이터 복원 회로로서,상기 수신 데이터 스트림의 채널 왜곡을 보상하는 입력 버퍼;상기 입력 버퍼로부터 수신한 상기 채널 왜곡이 보상된 수신 데이터 스트림이 복원 클럭보다 빠른지 아니면 느린지를 결정하는 샘플기;상기 수신 데이터 스트림의 UI(unit interval)을 고려하여 상기 복원 클럭을 생성하는 샘플링 클럭 생성부; 및상기 샘플기의 결정 값에 따라 상기 샘플링 클럭 생성부로부터 출력되는 상기 복원 클럭이 상기 수신 데이터 스트림의 UI(unit interval)의 중앙에 위치하도록 상기 복원 클럭의 위상을 보상하고, 상기 보상된 복원 클럭을 상기 샘플기로 제공하는 클럭 위상 보상기를 포함하는 클럭 및 데이터 복원 회로. |

| 2 | 제 1 항에 있어서, 상기 입력 버퍼로부터 출력된 상기 수신 데이터 스트림의 엣지 정보를 검출하여 상기 검출된 엣지 정보를 상기 샘플링 클럭 생성부로 제공하는 엣지 검출기를 더 포함하는 클럭 및 데이터 복원 회로. |

| 3 | 제 2 항에 있어서, 상기 엣지 검출기는상기 입력 버퍼로부터 출력된 상기 수신 데이터 스트림을 지연시키는 가변 지연 버퍼 소자; 및상기 입력 버퍼의 제 1 수신 데이터 스트림과 상기 가변 지연 버퍼 소자로부터 지연 출력되는 제 2 수신 데이터 스트림을 XOR 연산하여 엣지 펄스를 출력하는 XOR 게이트로 구성되는 클럭 및 데이터 복원 회로. |

| 4 | 제 2 항에 있어서, 상기 샘플링 클럭 생성부는 상기 검출된 엣지 정보에 기반하여 발진기의 지터 누적(jitter accumulation)을 리셋(reset)시키는 클럭 및 데이터 복원 회로. |

| 5 | 제 1 항에 있어서, 상기 샘플기는 뱅뱅 위상 검출기(Bang-Bang Phase Detector: BBPD), 알렉산더 위상 검출기(Alexander Phase Detector) 또는 호지 위상 검출기(Hogge Phase Detector)로 구성되는 클럭 및 데이터 복원 회로. |

| 6 | 제 1 항에 있어서,상기 샘플링 클럭 생성부는상기 복원 클럭에 대응하는 정수 N 배의 기준 클럭을 생성하는 주입 잠금 발진기(Injection-Locked Oscillator; ILO); 및상기 ILO로부터 출력된 클럭 신호를 피드백 받아 상기 정수 N 값을 결정하는 주파수 제어기를 포함하는 클럭 및 데이터 복원 회로. |

| 7 | 제 6 항에 있어서,상기 주파수 제어기는 주파수 획득(frequency acquisition) 및 주파수 트래킹(frequency tracking)을 수행하는 주파수 잠금 루프(frequency locked loop: FLL)로 구성되는 클럭 및 데이터 복원 회로. |

| 8 | 제 7 항에 있어서, 상기 FLL은상기 ILO로부터 출력되는 클럭을 1/N로 분주하는 분주기;상기 분주기로부터 분주된 클럭의 제 1 주파수와 상기 기준 클럭의 제 2 주파수를 비교하는 주파수 검출기(frequency detector: FD); 및상기 FD로부터 비교 결과를 기반으로 상기 ILO로부터 출력되는 클럭의 제 3주파수가 상기 기준 클럭의 제 2 주파수의 N 배가 되도록 제 1 디지털 코드를 상기 ILO로 제공하는 제 2 DLF(Digital Loop Filter)를 포함하며,상기 분주기-상기 주파수 검출기(FD)-상기 제 2 DLF는 적분 경로(integral path)를 형성하는 클럭 및 데이터 복원 회로. |

| 9 | 제 1 항에 있어서, 상기 클럭 위상 보상기는상기 샘플기로부터 샘플링 결과에 기반하여 제 2 디지털 코드를 생성하는 제1 DLF; 및상기 제 2 디지털 코드에 따라 상기 ILO로부터 출력되는 클럭의 위상을 빠르게 하거나 느리게 보상시키는 DCDL(Digitally Controlled Delay Line)를 포함하며,상기 제1 DLF와 상기 DCDL(Digitally Controlled Delay Line)는 비례 경로(proportional path)를 형성하는 클럭 및 데이터 복원 회로. |

| 10 | FTTH(Fiber To The Home), ATM(Asynchronous Transfer Mode), EPON(Ethernet Passive Optical Network), GPON(Gigabit Passive Optical Network), LANs(Local Area Networks), Gigabit Ethernet 중 적어도 하나를 위한 수신기로서,상기 수신기는 개시된 청구항 제1항의 클럭 및 데이터 복원 회로를 포함하는 수신기. |

| 11 | 수신 데이터 스트림의 채널 왜곡을 보상하는 단계;샘플링 클럭 생성부를 통해 상기 수신 데이터 스트림의 UI(unit interval)을 고려하여 복원 클럭을 생성하는 단계;샘플기를 통해 상기 입력 버퍼로부터 수신한 상기 채널 왜곡이 보상된 수신 데이터 스트림이 상기 복원 클럭보다 빠른지 아니면 느린지를 결정하는 단계; 및클럭 위상 보상기를 통해 상기 샘플기의 결정 값에 따라 상기 샘플링 클럭 생성부로부터 출력되는 상기 복원 클럭이 상기 수신 데이터 스트림의 UI(unit interval)의 중앙에 위치하도록 상기 복원 클럭의 위상을 보상하는 단계를 포함하는 클럭 및 데이터 복원 회로의 동작 방법. |

| 12 | 제 11 항에 있어서, 상기 입력 버퍼로부터 출력된 상기 수신 데이터 스트림의 엣지 정보를 검출하여 상기 검출된 엣지 정보를 상기 샘플링 클럭 생성부로 제공하는 단계를 더 포함하는 클럭 및 데이터 복원 회로의 동작 방법. |

| 13 | 제 12 항에 있어서, 상기 엣지 정보를 검출하는 단계는상기 입력 버퍼로부터 출력된 상기 수신 데이터 스트림을 지연시키는 단계; 및상기 입력 버퍼의 제 1 수신 데이터 스트림과 상기 가변 지연 버퍼 소자로부터 지연 출력되는 제 2 수신 데이터 스트림을 XOR 연산하여 엣지 펄스를 출력하는 단계를 포함하는 클럭 및 데이터 복원 회로의 동작 방법. |

| 14 | 제 11 항에 있어서, 상기 복원 클럭의 위상을 보상하는 단계는,주입 잠금 발진기(Injection-Locked Oscillator; ILO)를 통해 상기 복원 클럭에 대응하는 정수 N 배의 기준 클럭을 생성하는 단계; 및주파수 제어기를 통해 상기 ILO로부터 출력된 클럭 신호를 피드백 받아 상기 정수 N 값을 결정하는 단계를 포함하는 클럭 및 데이터 복원 회로. |

| 15 | 제 14 항에 있어서, 상기 정수 N 값을 결정하는 단계는분주기를 통해 상기 ILO로부터 출력되는 클럭을 1/N로 분주하는 단계;주파수 검출기(frequency detector: FD)를 통해 상기 분주기로부터 분주된 클럭의 제 1 주파수와 상기 기준 클럭의 제 2 주파수를 비교하는 단계; 및제 2 DLF를 통해 상기 FD로부터 비교 결과를 기반으로 상기 ILO로부터 출력되는 클럭의 제 3주파수가 상기 기준 클럭의 제 2 주파수의 N 배가 되도록 제 1 디지털 코드를 생성하는 단계를 포함하는 클럭 및 데이터 복원 회로의 동작 방법. |

| 16 | 제 11 항에 있어서, 상기 복원 클럭의 위상을 보상하는 단계는,제 1 DLF를 통해 상기 샘플기로부터 샘플링 결과에 기반하여 제 2 디지털 코드를 생성하는 단계; 및DCDL를 통해 상기 제 2 디지털 코드에 따라 상기 샘플링 클럭 생성부로부터 출력되는 클럭의 위상을 빠르게 하거나 느리게 보상시키는 단계를 포함하는 클럭 및 데이터 복원 회로의 동작 방법. |