| 번호 | 청구항 |

|---|---|

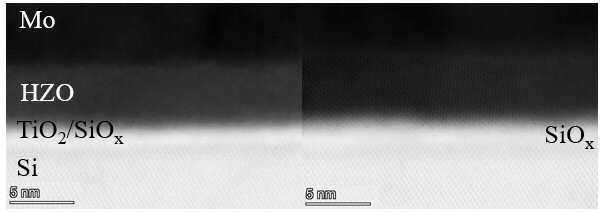

| 1 | 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터의 제조방법은(A) 두께 1nm 이하의 티타늄(Ti) 금속층을 실리콘(Si) 기판에 증착하는 단계; (B) 상기 티타늄(Ti) 금속층 위에 하프늄 지르코늄 옥사이드 박막 (Hf1-xZrxO2)을 증착하는 단계 - 상기 하프늄 지르코늄 옥사이드 박막 증착시 산소 공급원인 오존 (O3)에 의해 실리콘 기판 표면이 산화되어 실리콘 옥사이드 (SiOx) 계면층이 형성되고, 상기 티타늄(Ti) 금속층은 산소 공급원인 오존(O3)에 의해 고유전율 산화티타늄(TiO2) 층으로 산화됨 - ; (C) 하프늄 지르코늄 옥사이드 박막 위에 상부전극을 증착하는 단계 - 상기 상부전극의 재료는 몰리브데넘(Mo)이며, 증착 방법으로는 스퍼터링 시스템의 DC 반응성 스퍼터링(reactive sputtering)을 사용하고, 증착 조건은 플라즈마 파워(Plasma power) 150 W, 기본 압력 (Base pressure) 3 X 10-6 Torr, 공정 압력 (working pressure) 8 X 10-3 Torr의 조건으로 5분 동안 50 nm 증착함 - ; 를 포함하고,상기 상부전극의 모양을 결정하는 마스크(Shadow mask)는 직경 200μm의 구형 패턴을 사용하고(D) 급속 열처리 공정(RTP, Rapid Thermal Process)을 실행하는 단계 - 상기 급속 열처리 공정은 질소(N2) 대기(atmosphere)에서 500℃, 600℃ 또는 700℃의 온도로 30초의 조건으로 실행됨 - ; 를 포함하고상기 고유전율 산화티타늄(TiO2) 층은 실리콘(Si) 기판과 산화하프늄(HfO2) 기반 강유전체 층 사이 계면특성을 향상시키고상기 (A)의 단계; 는(A-1) 불산(HF)을 증류수에 희석시킨 5% 불산 수용액을 사용하여 BOE(Buffered Oxide Etch) 처리를 30초 실시하여 실리콘 기판 표면에 존재하는 SiO2를 제거하는 단계;(A-2) 티타늄 금속층 증착에 있어서, 티타늄(Ti) 희생층에 스퍼터링 시스템(Sputtering System)의 DC 반응 스퍼터링(Direct current reactive sputtering)을 사용하여, 플라즈마 파워(Plasma power) 100W, 기본 압력 (Base pressure) 3 X 10-6 Torr, 공정 압력 (working pressure) 5 X 10-3 Torr의 조건으로 5초 증착하는 단계; 를 포함하고상기 (B)의 단계; 는(B-1) Hf0.5Zr0.5O2 박막을 원자층 증착법(ALD, Atomic Layer Deposition)을 통해 기판온도 280 ℃에서 [(CH3)(C2H5)N]4Hf (TEMAH), [(CH3)(C2H5)N]4Zr (TEMAZ)을 금속 프리쿼서(Metal precursor)로 사용하고 산소 공급원으로 오존(O3)을 사용하여 박막의 두께를 3nm, 4nm 또는 5 nm로 증착하는 단계 - 상기 Hf0.5Zr0.5O2 박막은 산화하프늄과 산화지르코늄이 고용체 형태를 이룸 -; 를 포함하고,상기 (B-1) 단계에 의해 상기 산화하프늄과 산화지르코늄은 1:1 비율(Hf0.5Zr0.5O2)로 티타늄 금속층 위에 증착되고 증착된 산화하프늄과 산화지르코늄은 고용체의 형태를 이루고상부전극의 모양을 결정하는 마스크(Shadow mask)는 직경 200μm의 구형 패턴을 사용하는 것을 특징으로 하는 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터의 제조방법. |

| 2 | 삭제 |

| 3 | 삭제 |

| 4 | 삭제 |

| 5 | 삭제 |

| 6 | 삭제 |

| 7 | 실리콘 기판 및 하프늄 지르코늄 옥사이드 박막을 포함하는 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터에 있어서,두께 1nm 이하의 티타늄(Ti) 금속층이 실리콘(Si) 기판과 하프늄 지르코늄 옥사이드 박막 사이에 증착되고상기 증착된 티타늄(Ti) 금속층은 하프늄 지르코늄 옥사이드 박막의 원자층 증착 공정 중, 산소 공급원인 오존(O3)에 의해 고유전율 산화티타늄(TiO2) 층으로 산화되어 실리콘(Si) 기판과 산화하프늄(HfO2) 기반 강유전체 층 사이 계면특성을 향상시키고상기 실리콘 기판은 불산(HF)을 증류수에 희석시킨 5% 불산 수용액을 사용하여 BOE(Buffered Oxide Etch) 처리를 30초 실시하여, 표면에 존재하는 SiO2를 제거하고티타늄 금속층은 티타늄(Ti) 희생층에 스퍼터링 시스템(Sputtering System)의 DC(Direct current) 반응성 스퍼터링(reactive sputtering)을 사용하여 증착되고, 상기 스퍼터링에 의해 플라즈마 파워(Plasma power) 100W, 기본 압력(Base pressure) 3 X 10-6 Torr, 공정 압력 (working pressure) 5 X 10-3 Torr의 조건으로 5초 증착되고티타늄 금속층 위의 하프늄 지르코늄 옥사이드 박막은,상기 하프늄 지르코늄 옥사이드(Hf0.5Zr0.5O2) 박막을 원자층 증착법 (ALD, Atomic Layer Deposition)를 통해 기판온도 280 ℃에서 [(CH3)(C2H5)N]4Hf (TEMAH), [(CH3)(C2H5)N]4Zr (TEMAZ)을 금속 프리쿼서(Metal precursor)로 사용하고 산소 공급원으로 오존(O3)을 사용하여 박막 두께 3nm, 4nm 또는 5 nm로 증착되고, 상기 상기 하프늄 지르코늄 옥사이드(Hf0.5Zr0.5O2) 박막은 산화하프늄과 산화지르코늄이 고용체 형태를 이루며,증착이 끝난 하프늄 지르코늄 옥사이드 박막은 상기 산화하프늄과 산화지르코늄이 1:1 비율(Hf0.5Zr0.5O2)을 이루고 고용체의 형태를 이루고상기 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터는 하프늄 지르코늄 옥사이드 박막 위에 상부전극을 더 포함하며,상부전극의 재료는 몰리브데넘(Mo)이며, 상기 상부전극은 스퍼터링 시스템의 DC 반응성 스퍼터링(reactive sputtering)을 사용하여, 플라즈마 파워(Plasma power) 150 W, 기본 압력 (Base pressure) 3 X 10-6 Torr, 공정 압력 (working pressure) 8 X 10-3 Torr의 조건으로 5분 동안 50 nm 증착되고,상기 상부전극의 모양을 결정하는 마스크(Shadow mask)는 직경 200μm의 구형 패턴을 사용하고상기 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터는 급속 열처리 공정(RTP, Rapid Thermal Process)을 거치며, 상기 급속 열처리 공정은 질소(N2) 대기에서 500℃, 600℃ 또는 700 ℃의 온도로 30초의 조건으로 실행되고상부전극의 모양을 결정하는 마스크(Shadow mask)는 직경 200μm의 구형 패턴을 사용하는 것을 특징으로 하는 극박막 산화하프늄(HfO2) 유전층 기반 금속-강유전체-실리콘 커패시터. |

| 8 | 삭제 |

| 9 | 삭제 |

| 10 | 삭제 |

| 11 | 삭제 |

| 12 | 삭제 |