| 번호 | 청구항 |

|---|---|

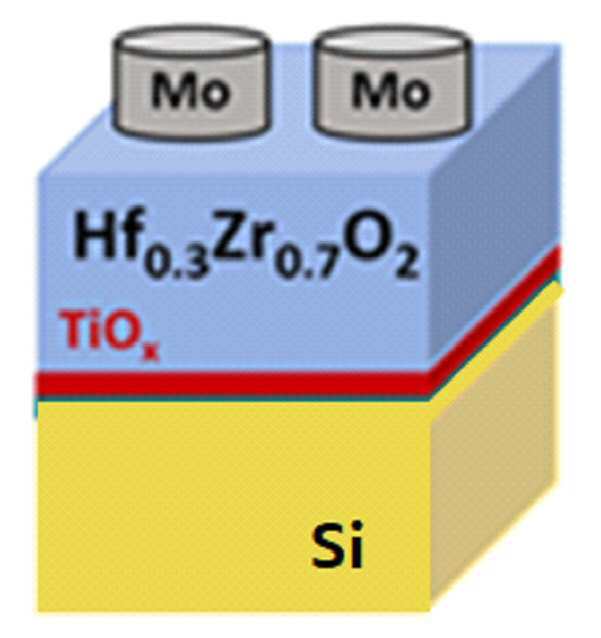

| 1 | 실리콘(silicon) 기판;상기 실리콘 기판 상에 형성된 티타늄 산화물 함유 희생층;상기 희생층 상에 형성된 하프늄-지르코늄 복합 산화물을 포함하는 유전층; 및상기 유전층 상에 형성된 금속계 전극;을 포함하고,상기 실리콘 기판은 SiOx(0003c#x≤2)로 표시되는 실리콘 산화물을 포함하지 않는 것이며,상기 하프늄-지르코늄 복합 산화물은 하기 화학식 1로 표시되는 것인, 커패시터.[화학식 1]Hf1-xZrxO2(0.5003c#x003c#1) |

| 2 | 삭제 |

| 3 | 청구항 1에 있어서,상기 희생층의 두께는 1.0 내지 3.0 nm인 것인, 커패시터. |

| 4 | 청구항 1에 있어서,상기 희생층은 산소 결핍(oxygen-deficient) 티타늄 산화물을 포함하지 않는 것인, 커패시터. |

| 5 | 청구항 1에 있어서,상기 유전층은 반강유전성(antiferroelectric)인 것인, 커패시터. |

| 6 | 삭제 |

| 7 | 청구항 1에 있어서,상기 유전층의 두께는 5 내지 15 nm인 것인, 커패시터. |

| 8 | 청구항 1에 있어서,상기 금속계 전극은 티타늄, 탈륨, 몰리브덴, 알루미늄 및 텅스텐으로 이루어진 군에서 선택되는 적어도 어느 하나의 금속 또는 그들의 질화물을 포함하는 것인, 커패시터. |

| 9 | 청구항 1에 있어서,상기 금속계 전극의 두께는 60 내지 80 nm인 것인, 커패시터. |

| 10 | 청구항 1, 청구항 3 내지 5 및 청구항 7 내지 9 중 어느 한 항의 커패시터를 포함하는, 반도체 소자. |

| 11 | i) 실리콘 기판 상에 제1 증착에 의해서 티타늄 함유 전구층을 형성시키는 단계;ii) 오존의 존재 하에 상기 전구층 상에 하프늄 전구체 화합물 및 지르코늄 전구체 화합물로부터의 제2 증착에 의해서, 하프늄-지르코늄 복합 산화물을 포함하는 유전층을 형성시키면서, 상기 오존에 의해서 상기 티타늄 함유 전구층이 티타늄 산화물 함유 희생층으로 변화되는 단계;iii) 상기 유전층 상에 제3 증착에 의해서 금속계 전극을 형성시키는 단계;를 포함하고,상기 i) 단계 이전에, 상기 실리콘 기판 표면에 존재하는 이산화규소(SiO2) 막을 제거하는 단계를 더 포함하는 것이며,상기 하프늄-지르코늄 복합 산화물은 하기 화학식 1로 표시되는 것인, 커패시터의 제조 방법.[화학식 1]Hf1-xZrxO2(0.5003c#x003c#1) |

| 12 | 삭제 |

| 13 | 청구항 11에 있어서,상기 i) 단계에서의 상기 제1 증착은 플라즈마 파워를 이용한 스퍼터링 방식으로 수행되는 것인, 커패시터의 제조 방법. |

| 14 | 청구항 11에 있어서,상기 희생층의 두께는 1.0 nm 내지 2.0 nm인 것인, 커패시터의 제조 방법. |

| 15 | 청구항 11에 있어서,상기 희생층은 산소 결핍(oxygen-deficient) 티타늄 산화물을 포함하지 않는 것인, 커패시터의 제조 방법. |

| 16 | 청구항 11에 있어서,상기 ii) 단계에서의 상기 제2 증착은 250 내지 300 ℃의 온도 하에서 수행되는 것인, 커패시터의 제조 방법. |

| 17 | 삭제 |

| 18 | 청구항 11에 있어서,상기 금속계 전극은 티타늄, 탈륨, 몰리브덴, 알루미늄 및 텅스텐으로 이루어진 군에서 선택되는 적어도 어느 하나의 금속 또는 그들의 질화물을 포함하는 것인, 커패시터의 제조 방법. |

| 19 | 청구항 11에 있어서,상기 iii) 단계에서의 제3 증착은 플라즈마 파워를 이용한 스퍼터링 방식으로 수행되는 것인, 커패시터의 제조 방법. |

| 20 | 청구항 11에 있어서,상기 iii) 단계 이후에, 금속화 후 어닐링(post metallization annealing) 단계를 더 포함하는 것인, 커패시터의 제조 방법. |