반도체 물질의 입계를 전하저장소로 이용하는 반도체 소자

SEMICONDUCTOR DEVICE USING GRAIN BOUNDARY OF SEMICONDUCTOR MATERIAL AS CHARGE-STORAGE NODE

특허 요약

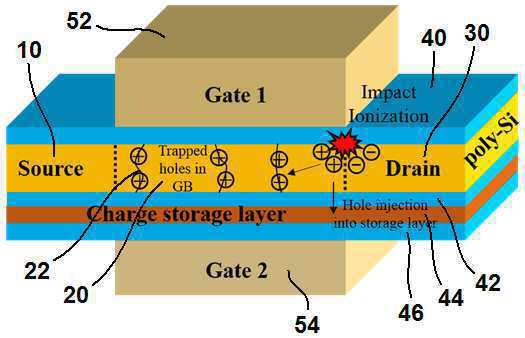

본 발명은 소스와 드레인 사이에 하나 이상의 입계(grain boundary)를 가진 플로팅 바디를 구비하고, 상기 입계를 전하저장소로 이용함으로써, 소자의 바디 두께가 최대 공핍층 두께보다 작아도 공핍층에서 생성된 과잉 홀이나 전자가 바디의 입계에 저장되어 1T DRAM 등의 휘발성 메모리 소자나 단기기억이 가능한 시냅스 모방 소자로 사용될 수 있고, 하나 이상의 입계를 가진 플로팅 바디를 사이에 두고 비대칭 제 1, 2 게이트를 형성함으로써, 휘발성 메모리와 비휘발성 메모리 소자를 동시 구현 가능하고, 전하저장층이 포함된 게이트 절연막 스택이 형성된 제 2 게이트를 통해 장기기억 전환이 가능한 시냅스 모방 소자를 구현할 수 있으며, 3차원 적층이 가능한 반도체 물질의 입계를 전하저장소로 이용하는 반도체 소자를 제공한다.

청구항

| 번호 | 청구항 |

|---|---|

| 1 | 특정 도전형 반도체 물질로 형성된 소스와 드레인;상기 소스와 드레인 사이에서 상기 도전형과 반대 타입의 반도체 물질로 형성되어 상기 소스와 드레인을 포함한 주변과 전기적으로 고립된 플로팅 바디;상기 플로팅 바디 상에 게이트 절연막을 사이에 두고 형성된 제 1 게이트를 포함하여 구성되되,상기 플로팅 바디는 상기 소스와 드레인 사이에 하나 이상의 입계(grain boundary)를 가지고, 상기 입계를 전하저장소로 이용하고,상기 드레인 또는 상기 소스 쪽의 공핍층에서 충격이온화로 생성되어 상기 입계에 저장되는 과잉 반송자는 상기 플로팅 바디에 채널을 형성하는 반송자와 반대 타입이고, 상기 입계에 저장된 과잉 반송자는 상기 채널을 형성하는 반송자에 대하여 입계의 전위장벽을 낮추는 것을 특징으로 하는 반도체 소자. |

| 2 | 제 1 항에 있어서,상기 플로팅 바디를 사이에 두고 상기 제 1 게이트와 마주보는 위치에 제 2 게이트가 더 형성된 것을 특징으로 하는 반도체 소자. |

| 3 | 제 2 항에 있어서,상기 플로팅 바디와 상기 제 2 게이트 사이에는 전하저장층이 포함된 게이트 절연막 스택이 형성된 것을 특징으로 하는 반도체 소자. |

| 4 | 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,상기 플로팅 바디는 다결정 반도체 물질로 형성된 것을 특징으로 하는 반도체 소자. |