| 번호 | 청구항 |

|---|---|

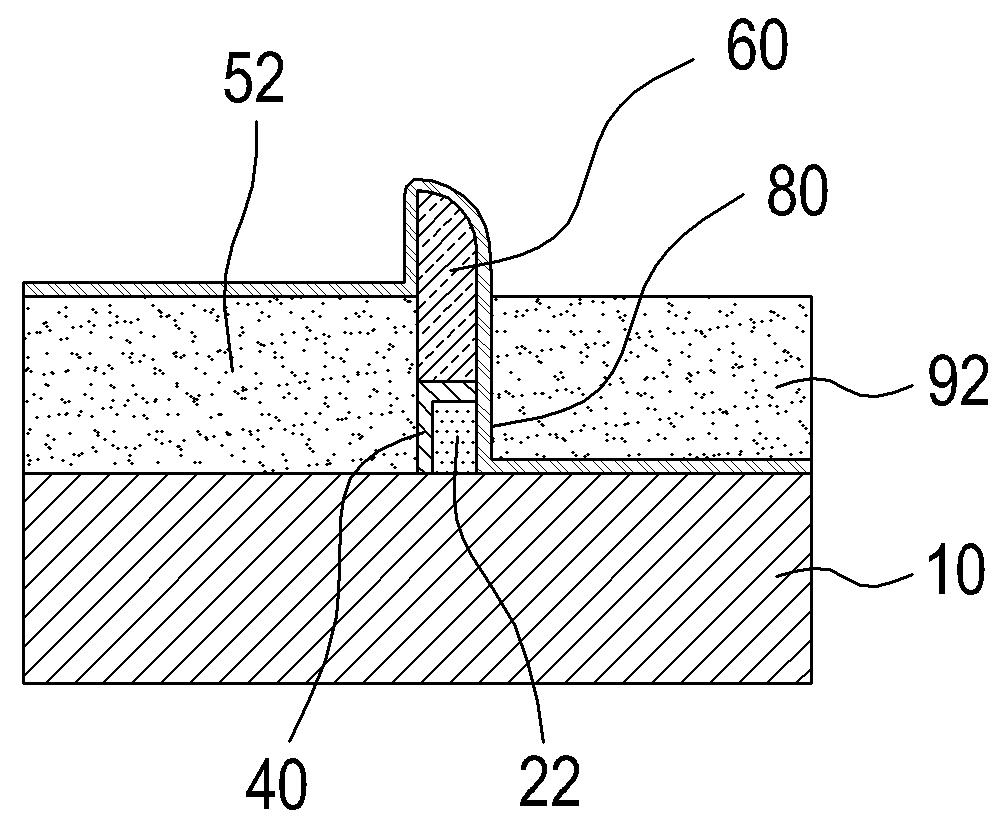

| 1 | 반도체 기판에 일정거리 이격된 소스 영역과 드레인 영역;상기 소스 영역과 상기 드레인 영역을 연결하는 핀 바디(fin body);상기 핀 바디의 일 측면으로 제 1 게이트 절연막을 사이에 두고 형성된 제 1 게이트;상기 핀 바디 상 및 상기 제 1 게이트의 일 측면에 형상된 절연막 측벽; 및상기 절연막 측벽 및 상기 핀 바디의 반대 측면 상에 제 2 게이트 절연막을 사이에 두고 형성된 제 2 게이트를 포함하여 구성되되,상기 제 1 게이트 절연막 및 상기 제 2 게이트 절연막 중 어느 하나는 단일 물질층으로 형성되고, 다른 하나는 전하저장층을 포함하는 2 이상 물질층의 적층구조로 형성된 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자. |

| 2 | 제 1 항에 있어서,상기 제 1 게이트 절연막은 실리콘산화막이고,상기 제 2 게이트 절연막은 산화막/나이트라이드(nitride)/산화막의 적층구조로 형성된 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자. |

| 3 | 제 1 항에 있어서,상기 소스 영역과 상기 드레인 영역은 서로 반대 도전형을 갖는 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자. |

| 4 | 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,상기 반도체 기판은 SOI 기판이고, 상기 제 1 게이트 및 상기 제 2 게이트 절연막은 매몰 절연막 상에 형성된 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자. |

| 5 | SOI 기판상에 하드마스크를 형성하고, 상기 SOI 기판의 실리콘층을 식각하여 제 1 게이트용 홈을 형성하는 제 1 단계;상기 제 1 게이트용 홈의 측면으로 드러난 상기 실리콘층을 산화시켜 제 1 게이트 산화막을 형성하고, 제 1 게이트 물질로 상기 제 1 게이트용 홈을 메워 제 1 게이트를 형성하는 제 2 단계;상기 하드마스크를 제거하는 제 3 단계;상기 SOI 기판상의 전면에 절연막을 증착하고 식각하여 상기 제 1 게이트의 측면으로 절연막 측벽을 형성하는 제 4 단계;상기 제 1 게이트의 일 측면과 마주하는 상기 실리콘층에 액티브 영역을 정의하기 위한 식각 마스크를 형성하는 제 5 단계;상기 식각 마스크로 상기 실리콘층을 식각하여 핀 바디(fin body)로 연결되는 액티브 영역을 형성하는 제 6 단계; 상기 SOI 기판상의 전면에 제 2 게이트 절연막 및 제 2 게이트 물질을 증착하고 식각하여 제 2 게이트를 형성하는 제 7 단계; 및상기 제 1 게이트 및 상기 제 2 게이트를 식각하여 상기 액티브 영역을 드러내고 이온 주입하여 소스/드레인 영역을 형성하는 제 8 단계를 포함하여 구성되되,상기 제 7 단계의 상기 제 2 게이트 절연막은 전하저장층을 포함하는 2 이상 물질층의 적층구조로 형성하는 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자의 제조방법. |

| 6 | 제 5 항에 있어서,상기 제 1 단계는 상기 제 1 게이트용 홈의 일측으로 제 1 게이트 컨택용 홈이 함께 형성되도록 하고,상기 제 2 단계는 상기 제 1 게이트 물질을 일정 두께로 증착한 후 상기 하드마스크가 드러나도록 평탄화 공정으로 식각하고, 상기 제 7 단계는 상기 제 2 게이트 물질을 일정 두께로 증착한 후 상기 제 2 게이트 절연막이 드러나도록 평탄화 공정으로 식각하는 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자의 제조방법. |

| 7 | 제 6 항에 있어서,상기 제 4 단계의 상기 절연막 측벽은 LPCVD로 산화막을 증착한 후 식각한 것으로 상기 제 6 단계에서 핀(fin) 바디 형성을 위한 식각 마스크로 사용되고,상기 제 5 단계의 상기 식각 마스크는 소스/드레인 영역 상에만 형성되는 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자의 제조방법. |

| 8 | 삭제 |

| 9 | 제 5 항 내지 제 7 항 중 어느 한 항에 있어서,상기 하드마스크는 상기 SOI 기판상에서 산화막과 나이트라이드(nitride)를 순차 적층시킨 것이고,상기 제 1 게이트 물질 및 상기 제 2 게이트 물질은 폴리 실리콘 또는 비정질 실리콘이고,상기 제 2 게이트 절연막은 산화막/나이트라이드/산화막의 적층구조로 형성하는 것을 특징으로 하는 비대칭 듀얼게이트 구조를 갖는 반도체소자의 제조방법. |