| 번호 | 청구항 |

|---|---|

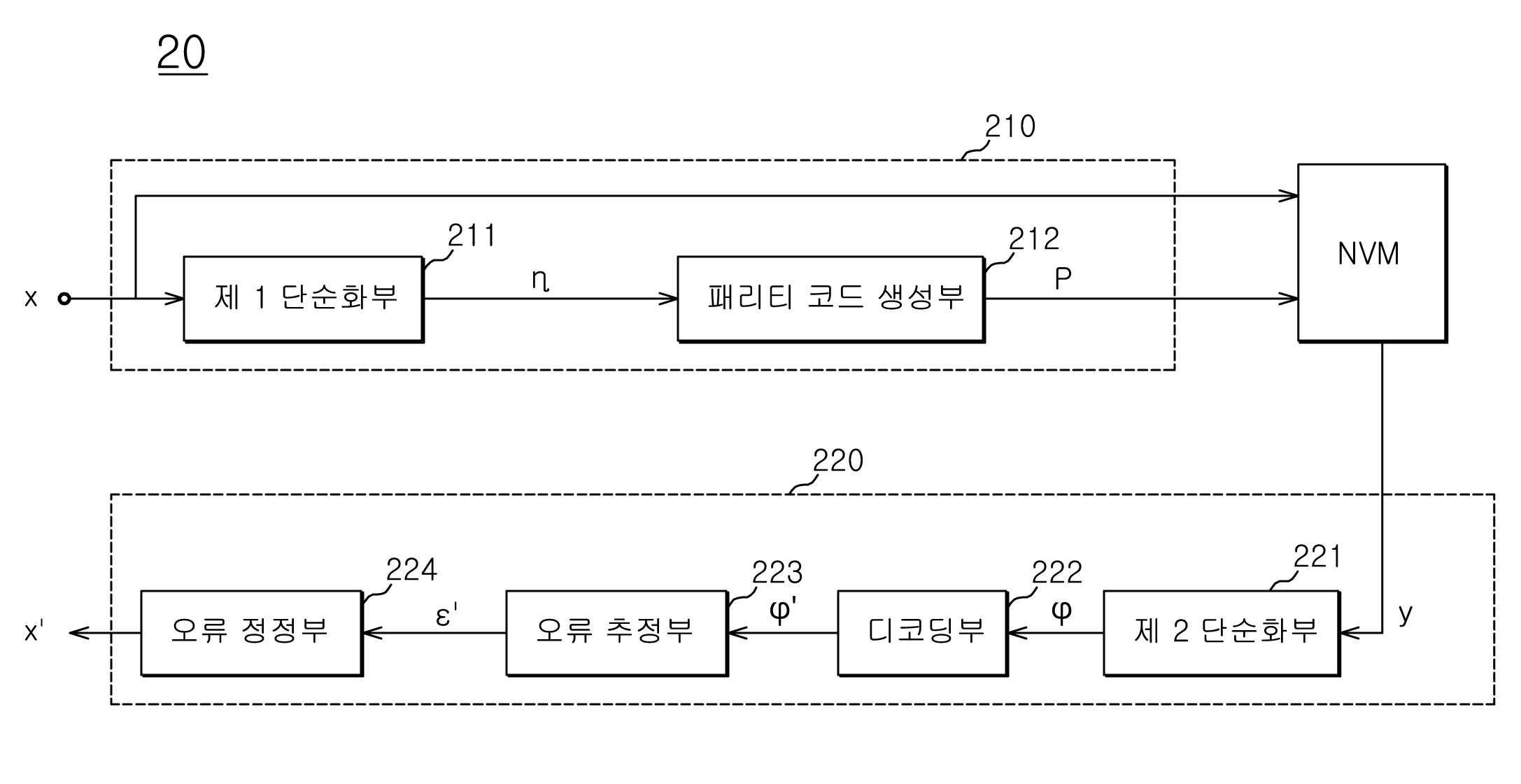

| 1 | 입력 데이터를 단순화하여 제 1 단순화 데이터를 생성하고, 상기 제 1 단순화 데이터를 기 설정된 베이스 에러 정정 코드로 부호화하여 패리티 코드를 생성하며, 상기 패리티 코드와 상기 입력 데이터의 항(ary) 수를 일치시킨 후 항(ary) 수가 일치된 상기 입력 데이터 및 상기 패리티 코드를 메모리 영역에 저장하는 인코더; 및상기 메모리 영역으로부터 에러를 포함할 수 있는 상기 입력 데이터 및 에러를 포함할 수 있는 상기 패리티 코드를 수신하고, 상기 에러를 포함할 수 있는 상기 입력 데이터를 단순화하여 제 2 단순화 데이터를 생성하며, 상기 제 2 단순화 데이터를 상기 베이스 에러 정정 코드로 복호화하고 오류를 정정하며, 상기 제 2 단순화 데이터와 상기 복호화 및 오류를 정정한 제 2 단순화 데이터를 기초로 오류값을 추정하고, 추정한 상기 오류값을 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터에 적용하여 오류가 정정된 데이터를 출력하는 디코더;를 포함하는 오류정정 회로. |

| 2 | 제 1 항에 있어서,상기 인코더는, 오류의 양방향 쉬프트 특성에 따라 기 설정된 단순화 인자에 따라 입력 데이터를 단순화하여 제 1 단순화 데이터를 생성하는 제 1 단순화부; 및기 설정된 상기 베이스 에러 정정 코드로 상기 제 1 단순화 데이터를 부호화하여 상기 패리티 코드를 생성하는 패리티 코드 생성부;를 포함하는 오류정정 회로. |

| 3 | 제 2 항에 있어서,상기 제 1 단순화부는 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 상기 입력 데이터를 모듈로 연산하여 상기 제 1 단순화 데이터를 생성하는 오류정정 회로. |

| 4 | 제 3 항에 있어서,상기 단순화 인자는 기 설정된 상기 상승방향 오류의 최대값(자연수)과 기 설정된 상기 하강방향 오류의 최대값(자연수)과 자연수 1의 합에 의해 결정되는 오류정정 회로. |

| 5 | 제 2 항에 있어서,상기 베이스 에러 정정 코드는 해밍(Hamming) 코드, BCH(Bose Chaudhuri Hocquenghem) 코드, RS(Reed-Solomon) 코드, 임의의 에러정정 코드 중 어느 하나인 오류정정 회로. |

| 6 | 제 1 항에 있어서,상기 디코더는, 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터를 오류의 양방향 쉬프트 특성에 따라 기 설정된 단순화 인자에 따라 단순화하여 상기 제 2 단순화 데이터를 생성하는 제 2 단순화부;상기 베이스 에러 정정 코드를 이용하여, 상기 제 2 단순화 데이터를 복호화하고 상기 복호화한 제 2 단순화 데이터의 오류를 정정하는 디코딩부;상기 제 2 단순화 데이터와, 상기 복호화 및 오류를 정정한 제 2 단순화 데이터를 기초로 상기 오류값을 추정하는 오류 추정부; 및추정한 상기 오류값을 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터에 적용하여 오류가 정정된 데이터를 출력하는 오류 정정부;를 포함하는 오류정정 회로. |

| 7 | 제 6 항에 있어서,상기 제 2 단순화부는, 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 상기 에러를 포함할 수 있는 상기 입력 데이터를 모듈로 연산하여 상기 제 2 단순화 데이터를 생성하는 오류정정 회로. |

| 8 | 제 6 항에 있어서,상기 베이스 에러 정정 코드는 해밍(Hamming) 코드, BCH(Bose Chaudhuri Hocquenghem) 코드, RS(Reed-Solomon) 코드, 임의의 에러정정 코드 중 어느 하나인 오류정정 회로. |

| 9 | 비휘발성 메모리 장치의 오류정정 방법으로서,데이터 저장 명령에 응답하여, 입력 데이터를 단순화하여 제 1 단순화 데이터를 생성하는 단계;상기 제 1 단순화 데이터를 기 설정된 베이스 에러 정정 코드로 부호화하여 패리티 코드를 생성하고, 상기 입력 데이터와 상기 패리티 코드의 항(ary) 수를 일치시키는 단계; 및상기 항(ary) 수가 일치된 입력 데이터 및 상기 패리티 코드를 메모리 영역에 저장하는 단계;를 포함하는 오류정정 방법. |

| 10 | 제 9 항에 있어서,데이터 독출 명령에 응답하여, 상기 메모리 영역으로부터 에러를 포함할 수 있는 상기 입력 데이터 및 에러를 포함할 수 있는 상기 패리티 코드를 수신하는 단계;상기 에러를 포함할 수 있는 상기 입력 데이터를 오류의 양방향 쉬프트 특성에 따라 기 설정된 단순화 인자에 따라 단순화하여 제 2 단순화 데이터를 생성하는 단계;상기 제 2 단순화 데이터를 상기 베이스 에러 정정 코드로 복호화하고 상기 복호화된 제 2 단순화 데이터의 오류를 정정하는 단계;상기 제 2 단순화 데이터와, 상기 복호화 및 오류를 정정한 제 2 단순화 데이터를 기초로 오류값을 추정하는 단계; 및추정한 상기 오류값을 상기 에러를 포함할 수 있는 상기 입력 데이터에 적용하여 오류가 정정된 데이터를 출력하는 단계;를 포함하는 오류정정 방법. |

| 11 | 제 10 항에 있어서,상기 제 1 단순화 데이터를 생성하는 단계는, 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 상기 입력 데이터를 모듈로 연산하는 단계인 오류정정 방법. |

| 12 | 제 10 항에 있어서,상기 제 2 단순화 데이터를 생성하는 단계는, 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 상기 에러를 포함할 수 있는 상기 입력 데이터를 모듈로 연산하는 단계인 오류정정 방법. |

| 13 | 제 11 항 또는 제 12 항 중 어느 하나의 항에 있어서,상기 단순화 인자는 기 설정된 상기 상승방향 오류의 최대값(자연수)과 기 설정된 상기 하강방향 오류의 최대값(자연수)과 자연수 1의 합에 의해 결정되는 오류정정 방법. |

| 14 | 제 10 항에 있어서,상기 베이스 에러 정정 코드는 해밍(Hamming) 코드, BCH(Bose Chaudhuri Hocquenghem) 코드, RS(Reed-Solomon) 코드, 임의의 에러정정 코드 중 어느 하나인 오류정정 방법. |

| 15 | 적어도 하나의 비휘발성 메모리 칩을 포함하는 메모리 영역;호스트 및 상기 메모리 영역 사이에 접속되는 메모리 제어기; 포함하고,상기 메모리 제어기는, 입력 데이터를 단순화하여 제 1 단순화 데이터를 생성하고, 상기 제 1 단순화 데이터를 기 설정된 베이스 에러 정정 코드로 부호화하여 패리티 코드를 생성하고 상기 입력 데이터와 상기 패리티 코드의 항(ary) 수를 일치시키며. 상기 항(ary) 수가 일치된 입력 데이터 및 상기 패리티 코드를 메모리 영역에 저장하는 인코더; 및상기 메모리 영역으로부터 에러를 포함할 수 있는 상기 입력 데이터 및 에러를 포함할 수 있는 상기 패리티 코드를 수신하고, 에러를 포함할 수 있는 상기 입력 데이터를 단순화하여 제 2 단순화 데이터를 생성하며, 상기 제 2 단순화 데이터를 상기 베이스 에러 정정 코드로 복호화하고 오류를 정정하며, 상기 제 2 단순화 데이터와 상기 복호화 및 오류를 정정한 제 2 단순화 데이터를 기초로 오류값을 추정하고, 추정한 상기 오류값을 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터에 적용하여 오류가 정정된 데이터를 출력하는 디코더;를 구비하는 오류정정 회로를 포함하는 비휘발성 메모리 장치. |

| 16 | 제 15 항에 있어서,상기 인코더는, 상기 입력 데이터를 오류의 양방향 쉬프트 특성에 따라 기 설정된 단순화 인자에 따라 단순화하여 제 1 단순화 데이터를 생성하는 제 1 단순화부; 및기 설정된 상기 베이스 에러 정정 코드로 상기 입력 데이터를 부호화하여 상기 패리티 코드를 생성하는 패리티 코드 생성부;를 포함하는 비휘발성 메모리 장치. |

| 17 | 제 15 항에 있어서,상기 디코더는, 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터를 오류의 양방향 쉬프트 특성에 따라 기 설정된 단순화 인자에 따라 단순화하여 제 2 단순화 데이터를 생성하는 제 2 단순화부;상기 베이스 에러 정정 코드를 이용하여, 상기 제 2 단순화 데이터를 복호화하고 상기 복호화한 제 2 단순화 데이터의 오류를 정정하는 디코딩부;상기 제 2 단순화 데이터와, 상기 복호화 및 오류를 정정한 제 2 단순화 데이터를 기초로 상기 오류값을 추정하는 오류 추정부; 및추정한 상기 오류값을 상기 메모리 영역으로부터 수신한 에러를 포함할 수 있는 상기 입력 데이터에 적용하여 오류가 정정된 데이터를 출력하는 오류 정정부;를 포함하는 비휘발성 메모리 장치. |

| 18 | 제 16 항에 있어서,상기 제 1 단순화부는 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 상기 입력 데이터를 모듈로 연산하여 상기 제 1 단순화 데이터를 생성하는 비휘발성 메모리 장치. |

| 19 | 제 17 항에 있어서,상기 제 2 단순화부는, 기 설정된 상승방향 오류의 크기 및 기 설정된 하강방향 오류의 크기에 기초하여 설정된 상기 단순화 인자에 따라 에러를 포함할 수 있는 상기 입력 데이터를 모듈로 연산하여 상기 제 2 단순화 데이터를 생성하는 비휘발성 메모리 장치. |

| 20 | 제 18 항 또는 제 19 항 중 어느 하나의 항에 있어서,상기 단순화 인자는 기 설정된 상기 상승방향 오류의 최대값(자연수)과 기 설정된 상기 하강방향 오류의 최대값(자연수)과 자연수 1의 합에 의해 결정되는 비휘발성 메모리 장치. |

| 21 | 제 15 항에 있어서,상기 베이스 에러 정정 코드는 해밍(Hamming) 코드, BCH(Bose Chaudhuri Hocquenghem) 코드, RS(Reed-Solomon) 코드, 임의의 에러정정 코드 중 어느 하나인 비휘발성 메모리 장치. |