| 번호 | 청구항 |

|---|---|

| 5 | 제2항 내지 제4항 중 어느 하나의 항에 있어서, 상기 상부전극 상에 하나 이상의 유전막과 하나 이상의 전극이 교번적으로 적층되어 있는 특징으로 하는 커패시터. |

| 6 | 제2항 내지 제4항 중 어느 하나의 항에 있어서, 상기 복수의 관통홀의 직경은 0.5 내지 10μm인 것을 특징으로 하는 커패시터. |

| 7 | 제2항 내지 제4항 중 어느 하나의 항에 있어서, 상기 하부전극 및 상기 상부전극은 Pt, Ru, Ir, Au, Ni, Mo, W, Al, Ta, Ag 및 Ti로 구성된 그룹으로부터 선택된 적어도 하나의 금속으로 이루어지거나, Pt, Ru, Sr, La, Ir, Au, Ni, Co, Mo, W, Al, Ta 및 Ti로 구성된 그룹으로부터 선택된 적어도 하나의 금속의 전도성 산화물 또는 전도성 질화물로 이루어진 것을 특징으로 하는 커패시터. |

| 1 | 삭제 |

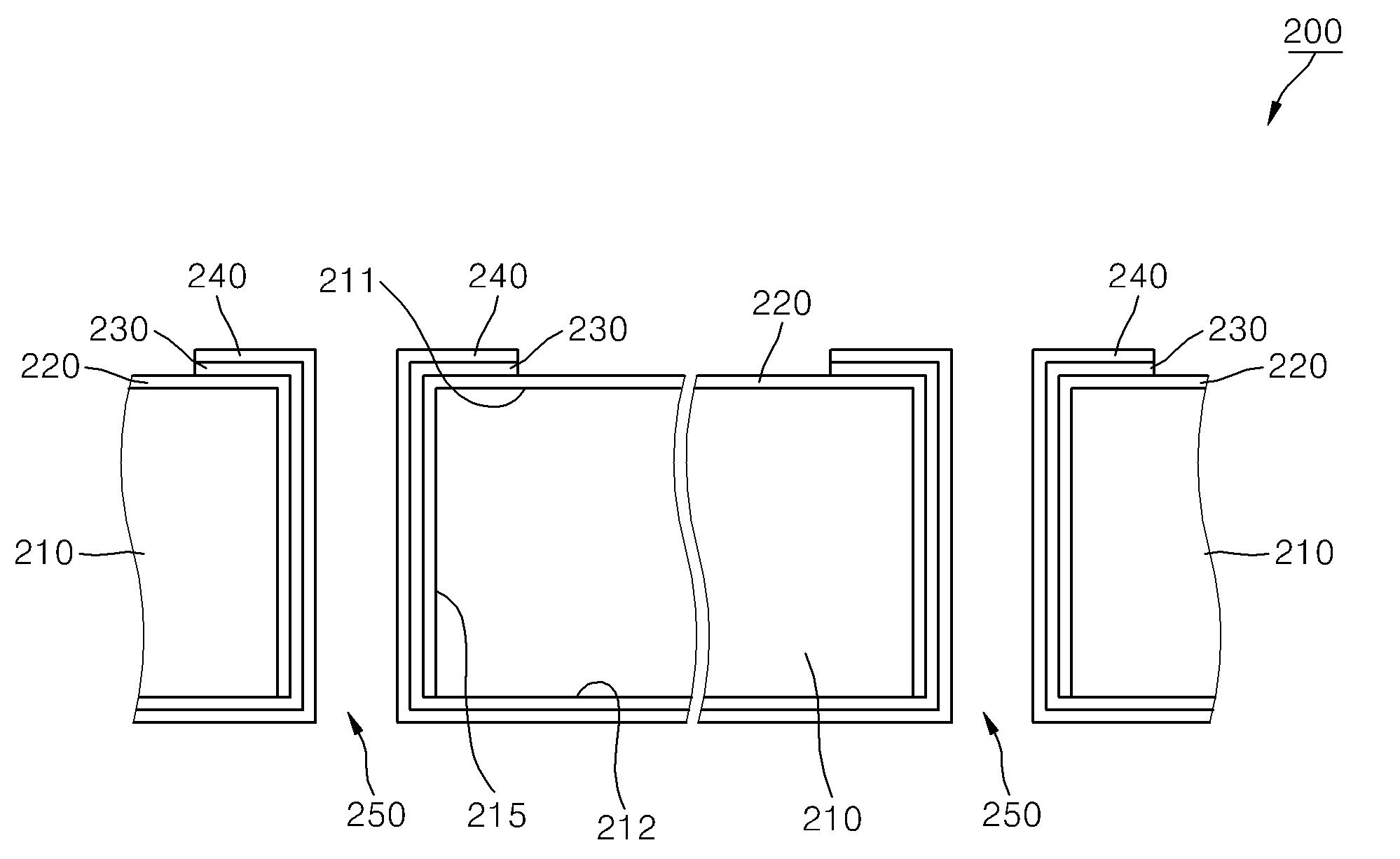

| 2 | 상면과 하면 사이를 관통하는 복수의 관통홀이 형성되어 있는 기판; 상기 복수의 관통홀의 내측면 상에 형성된 하부전극; 상기 하부전극 상에 형성된 유전막; 및 상기 유전막 상에 형성된 상부전극;을 포함하고, 상기 하부전극은 상기 복수의 관통홀의 내측면과 상기 기판의 상면이 함께 덮이도록 형성되며, 상기 유전막은 상기 하부전극과 상기 기판의 하면이 함께 덮이도록 형성되는 것을 특징으로 하는 커패시터. |

| 3 | 상면과 하면 사이를 관통하는 복수의 관통홀이 형성되어 있는 기판; 상기 복수의 관통홀의 내측면 상에 형성된 하부전극; 상기 하부전극 상에 형성된 유전막; 및 상기 유전막 상에 형성된 상부전극;을 포함하고, 하나의 관통홀이 최인접된 2개의 관통홀과 이루는 각도가 60°의 배수가 되도록, 상기 복수의 관통홀이 배치되어 있는 것을 특징으로 하는 커패시터. |

| 4 | 상면과 하면 사이를 관통하는 복수의 관통홀이 형성되어 있는 기판; 상기 복수의 관통홀의 내측면 상에 형성된 하부전극; 상기 하부전극 상에 형성된 유전막; 및 상기 유전막 상에 형성된 상부전극;을 포함하고, 하나의 관통홀이 최인접된 2개의 관통홀과 이루는 각도가 90°의 배수가 되도록, 상기 복수의 관통홀이 배치되어 있는 것을 특징으로 하는 커패시터. |

| 8 | 제2항 내지 제4항 중 어느 하나의 항에 있어서, 상기 유전막은 TiO2, ZrO2, Al2O3, Ta2O5, Nb2O5, HfO2, SrTiO3, BaTiO3, (Ba, Sr)TiO3, PbTiO3, SrBi2Ta2O9, (Pb,La)(Zr,Ti)O3 및 Pb(Zr, Ti)O3로 구성된 그룹으로부터 선택된 하나 이상의 고유전율 물질 또는 이에 도펀트를 첨가한 물질로 이루어진 것을 특징으로 하는 커패시터. |

| 9 | 삭제 |

| 10 | 기판의 상면과 하면 사이를 관통하는 복수의 관통홀을 형성하는 단계; 상기 기판을 반응기 내부의 기판 지지대에 로딩하는 단계; 상기 복수의 관통홀의 내측면 상에 하부전극을 형성하는 단계; 상기 하부전극 상에 유전막을 형성하는 단계; 상기 유전막 상에 상부전극을 형성하는 단계;를 포함하고, 상기 복수의 관통홀을 형성하는 단계는, 상기 기판의 상면에 패터닝된 마스크를 형성하는 단계; 상기 마스크를 이용하여 깊은 활성 이온 식각(deep reactive ion etching)법을 통해, 상기 기판의 상면에 복수의 홀을 형성하는 단계; 상기 복수의 홀의 내측벽을 산화시키는 단계; 상기 마스크와 상기 산화된 내측벽을 제거하는 단계; 및 상기 기판의 상면과 하면이 관통되도록, 상기 기판의 하면을 그라인딩(grinding)하는 단계;를 포함하는 것을 특징으로 하는 커패시터 제조방법. |

| 11 | 제10항에 있어서, 상기 복수의 관통홀을 통과하는 가스의 흐름이 원활하도록, 상기 기판 지지대는 상기 기판의 외주부를 지지하는 것을 특징으로 하는 커패시터 제조방법. |

| 12 | 제11항에 있어서, 상기 하부전극을 형성하는 단계, 유전막을 형성하는 단계 및 상부전극을 형성하는 단계는, 상기 기판의 상면과 수직한 방향으로 각각의 원료가스를 공급하는 것을 특징으로 하는 커패시터 제조방법. |

| 13 | 제10항에 있어서, 상기 하부전극, 상기 유전막 및 상기 상부전극은 원자층증착(Atomic Layer Deposition, ALD)법을 통해 형성하는 것을 특징으로 하는 커패시터 제조방법. |

| 14 | 제10항에 있어서, 상기 하부전극은 상기 복수의 관통홀의 내측면과 상기 기판의 상면이 함께 덮이도록 형성하며, 상기 유전막은 상기 하부전극과 상기 기판의 하면이 함께 덮이도록 형성하는 것을 특징으로 하는 커패시터 제조방법. |