| 번호 | 청구항 |

|---|---|

| 1 | 하나 이상의 프로세서들, 및상기 하나 이상의 프로세서들에 의해 실행되는 하나 이상의 프로그램들을 저장하는 메모리를 구비한 컴퓨팅 시스템에서 수행되는 방법으로서,복수의 인공 신경망 아키텍처 중 어느 하나를 백본 아키텍처로 수신하는 단계; 상기 백본 아키텍처를 기반으로 DCIM(Digital Computing-in-Memory) 매크로의 구조를 결정하는 단계;제1 알고리즘을 기반으로 상기 DCIM 매크로의 근사 덧셈 후보군을 생성하는 단계;상기 DCIM 매크로의 구조 및 상기 근사 덧셈 후보군을 기반으로 이기종 근사 DCIM을 생성하는 단계; 및제2 알고리즘을 기반으로 상기 이기종 근사 DCIM의 출력 채널 각각에 대해 근사 덧셈 후보군 중 적어도 하나를 매핑하는 단계를 포함하는 컴퓨팅 시스템의 동작 방법. |

| 2 | 제1항에 있어서,상기 근사 덧셈 후보군을 생성하는 단계는,입력 또는 가중치의 양자화 비트에 대해 분할 근사 덧셈을 수행하여 비트 그룹을 생성하고, 상기 비트 그룹에 대응되는 근사 덧셈의 표현 정보인 유전자를 판별하는 컴퓨팅 시스템의 동작 방법. |

| 3 | 제2항에 있어서,상기 근사 덧셈 후보군을 생성하는 단계는,진화 알고리즘을 상기 제1 알고리즘으로 이용하고, 상기 유전자를 변이 및 교차하여 상기 근사 덧셈 후보군을 생성하는 컴퓨팅 시스템의 동작 방법. |

| 4 | 제1항에 있어서,상기 채널 별 가중치를 매핑하는 단계는,유전 알고리즘을 상기 제2 알고리즘으로 이용하는 컴퓨팅 시스템의 동작 방법. |

| 5 | 제1항에 있어서,백본 아키텍처로 수신하는 단계는,상기 백본 아키텍처의 입력 및 가중치의 양자화 비트, 상기 백본 아키텍처의 적합도 및 상기 컴퓨팅 시스템의 목표치를 입력 데이터로 수신하는 컴퓨팅 시스템의 동작 방법. |

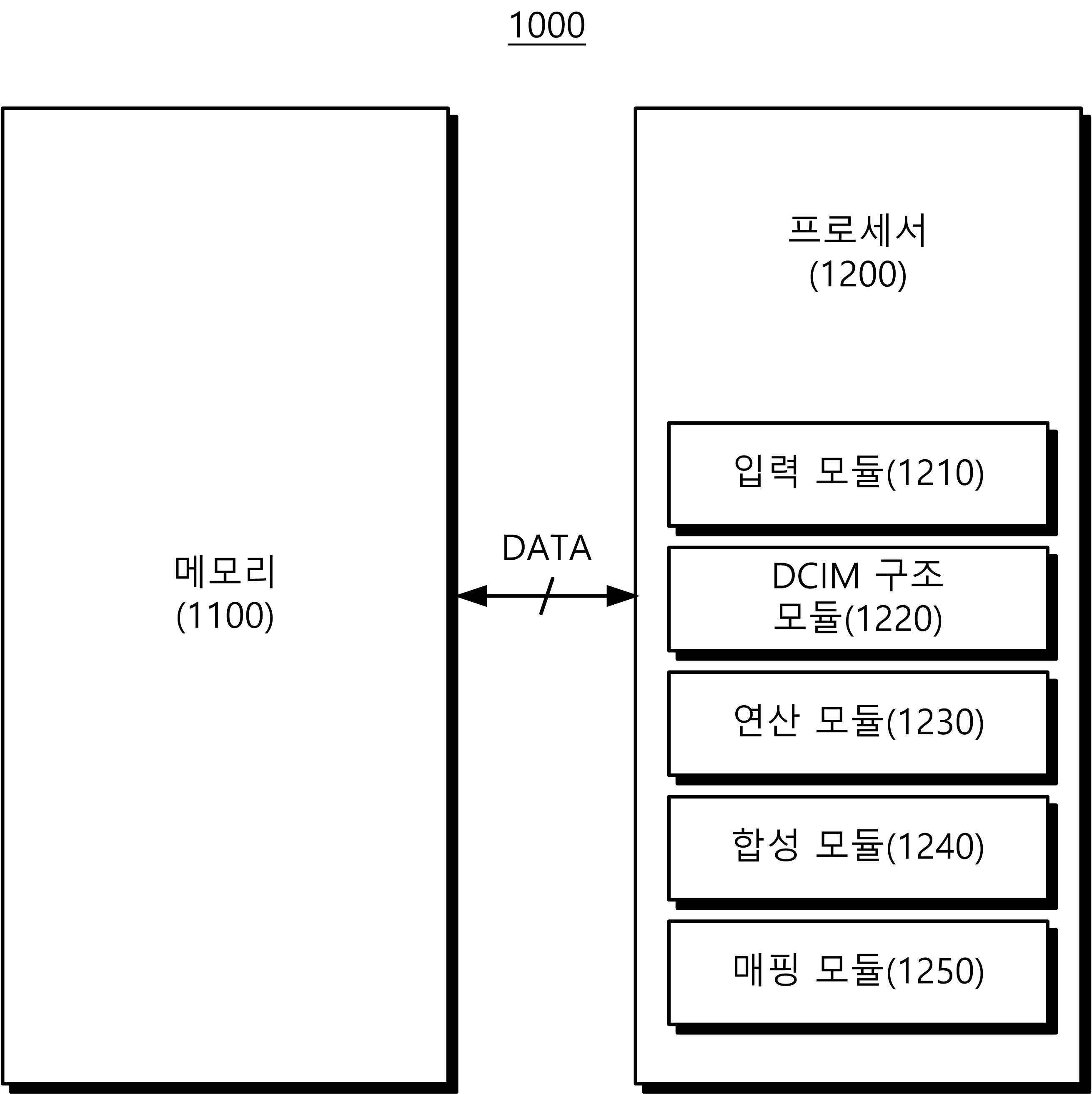

| 6 | 복수의 인공 신경망 아키텍처 중 어느 하나를 백본 아키텍처로 수신하는 입력 모듈; 상기 백본 아키텍처를 기반으로 DCIM(Digital Computing-in-Memory) 매크로의 구조를 결정하는 DCIM 구조 모듈;제1 알고리즘을 기반으로 상기 DCIM 매크로의 근사 덧셈 후보군을 생성하는 연산 모듈;상기 DCIM 매크로의 구조 및 상기 근사 덧셈 후보군을 기반으로 이기종 근사 DCIM을 생성하는 합성 모듈; 및제2 알고리즘을 기반으로 상기 이기종 근사 DCIM의 출력 채널 각각에 대해 상기 근사 덧셈 후보군 중 적어도 하나를 매핑하는 매핑 모듈을 포함하는 컴퓨팅 시스템. |

| 7 | 제6항에 있어서,상기 연산 모듈은,입력 또는 가중치의 양자화 비트에 대해 분할 근사 덧셈을 수행하여 비트 그룹을 생성하고, 상기 비트 그룹에 대응되는 근사 덧셈의 표현 정보인 유전자를 판별하는 컴퓨팅 시스템. |

| 8 | 제7항에 있어서,상기 연산 모듈은,진화 알고리즘을 상기 제1 알고리즘으로 이용하고, 상기 유전자를 변이 및 교차하여 상기 근사 덧셈 후보군을 생성하는 컴퓨팅 시스템. |

| 9 | 제6항에 있어서,상기 매핑 모듈은,유전 알고리즘을 상기 제2 알고리즘으로 이용하는 컴퓨팅 시스템. |

| 10 | 제6항에 있어서,상기 입력 모듈은,상기 백본 아키텍처의 입력 및 가중치의 양자화 비트, 상기 백본 아키텍처의 적합도 및 상기 컴퓨팅 시스템의 목표치를 입력 데이터로 수신하는 컴퓨팅 시스템. |