| 번호 | 청구항 |

|---|---|

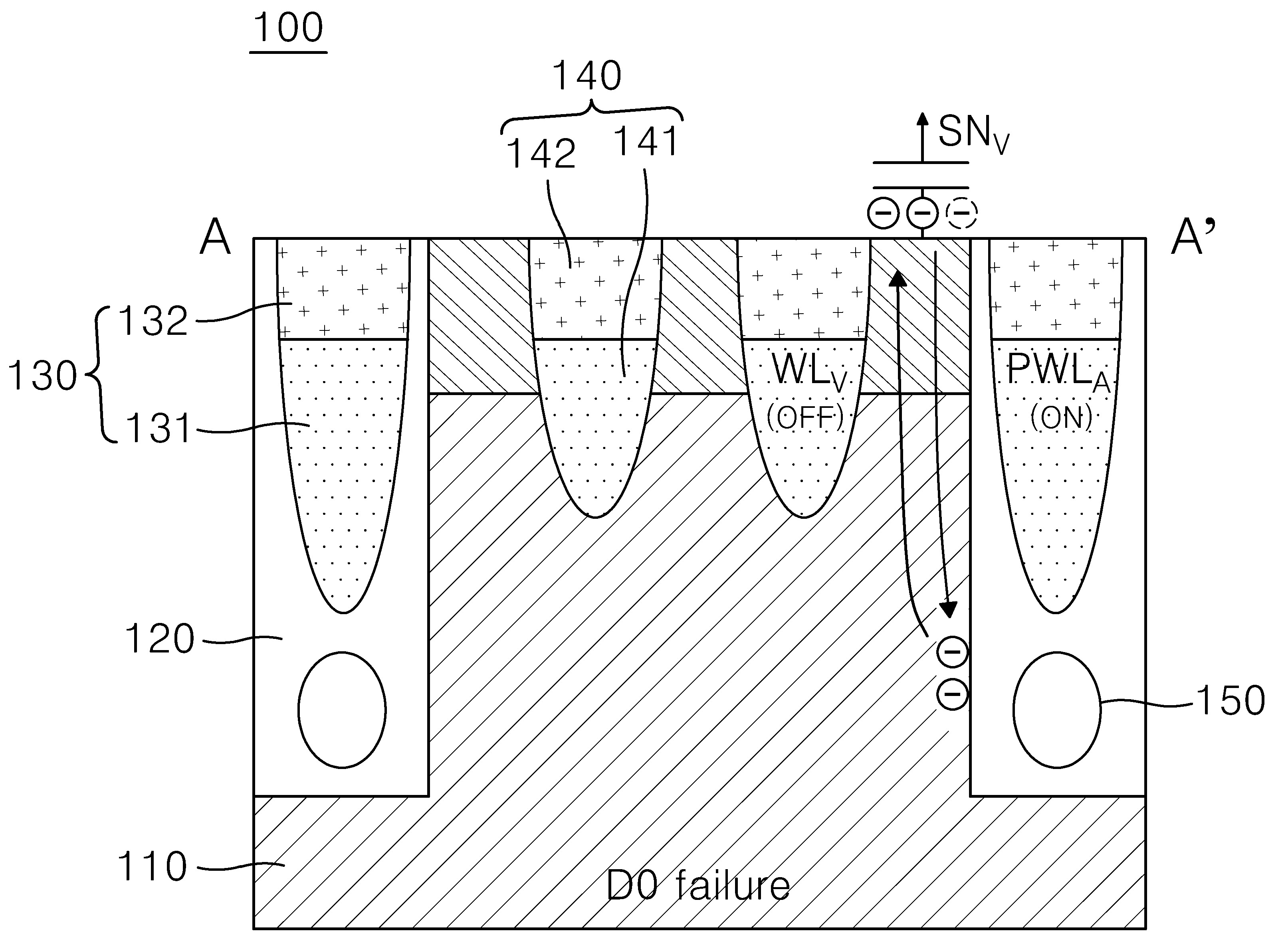

| 1 | 기판;상기 기판 내에서 수직방향으로 연장 형성되는 소자 분리막;상기 소자 분리막 내에서 수직방향으로 연장 형성되는 제1 게이트 구조체; 및상기 소자 분리막과 수평방향으로 이격되고, 상기 기판 내에서 수직방향으로 연장 형성되는 제2 게이트 구조체를 포함하되,상기 소자 분리막 내 상기 제1 게이트 구조체 하부에는 상기 소자 분리막의 계면에 접하지 않는 중공의 포켓이 형성되는반도체 메모리 장치. |

| 2 | 제1항에 있어서,상기 소자 분리막은 절연 물질로 이루어지는반도체 메모리 장치. |

| 3 | 제1항에 있어서,상기 제1 게이트 구조체는 DRAM(Dynamic Random Access Memory)을 구성하는 패싱 워드 라인(passing wordline)의 게이트 전극을 포함하는반도체 메모리 장치. |

| 4 | 제1항에 있어서,상기 중공의 포켓은, 상기 제1 게이트 구조체 하부에서 상기 소자 분리막에 의해 둘러싸인반도체 메모리 장치. |

| 5 | 제1항에 있어서,상기 중공의 포켓에는 상기 소자 분리막과는 다른 물질이 충진되는반도체 메모리 장치. |

| 6 | 제1항에 있어서,상기 중공의 포켓에는 상기 소자 분리막보다 낮은 유전율의 물질이 충진되는반도체 메모리 장치. |

| 7 | 제1항에 있어서,상기 중공의 포켓에는 공기(air)가 충진되는반도체 메모리 장치. |

| 8 | 제1항에 있어서,상기 중공의 포켓은,기판을 에칭(etching)하여 트랜치(trench)를 형성하는 단계; 및상기 트랜치의 내부가 전부 채워지지 않은 상태에서 상기 트랜치의 입구 양단에 형성되는 오버행(overhang) 영역이 접할 때까지 상기 트랜치를 소자 분리막을 이루는 물질로 증착하는 단계;에 의해 형성되는반도체 메모리 장치. |