| 번호 | 청구항 |

|---|---|

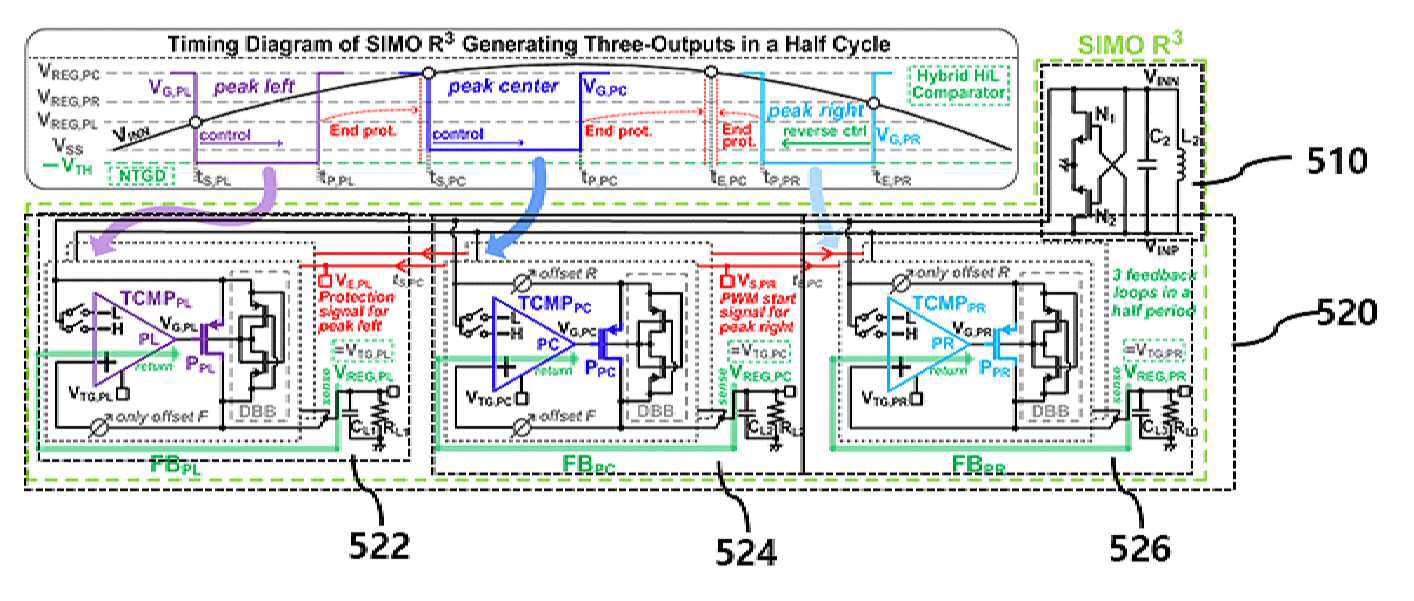

| 1 | 무선 전력 AC 신호를 반파장 입력 신호(VINN, VINP)로 변환하는 변환 회로부; 및상기 변환 회로부를 통해 입력되는 상기 반파장 입력 신호(VINN)를 기초로 각 반파장내의 서로 다른 다수의 영역에서 다수의 게이트 신호를 생성함으로써 반파장내에서 다수의 출력을 생성하는 출력 생성 회로부를 포함하는 단일-입력 다중-출력 공진 조정 정류기. |

| 2 | 제1 항에 있어서, 상기 변환 회로부는, 상기 무선 전력 AC 신호를 수신하는 공진 회로부(L2C2); 및상기 공진부(L2C2)에 병렬로 연결되되, 교차 결합된(cross coupled) 한 쌍의 트랜지스터(N1, N2)를 포함하되,상기 교차 결합된(cross coupled) 한 쌍의 트랜지스터(N1, N2)는 상기 공진 회로부(L2C2)를 통해 입력되는 상기 무선 전력 AC 신호를 반파장 입력 신호(VINN, VINP)로 변환하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 3 | 제1 항에 있어서, 상기 출력 생성 회로부는,제1 영역에서 상기 변환 회로부를 통해 출력되는 신호를 이용하여 제1 기준 신호(VREF,PL)를 생성하고, 상기 반파장 입력 신호(VINN)와 제1 기준 신호(VREF,PL)를 이용하여 제1 게이트 신호(VG,PL)를 생성하는 제1 출력 회로부;제2 영역에서 상기 변환 회로부를 통해 출력되는 신호를 이용하여 제2 기준 신호(VREF,PC)를 생성하고, 상기 반파장 입력 신호(VINN)와 제2 기준 신호(VREF,PC)를 이용하여 제2 게이트 신호(VG,PC)를 생성하는 제2 출력 회로부; 및제3 영역에서 상기 변환 회로부를 통해 출력되는 신호를 이용하여 제3 기준 신호(VREF,PR)를 생성하고, 상기 반파장 입력 신호(VINN)와 제3 기준 신호(VREF,PR)를 이용하여 제3 게이트 신호(VG,PR)를 생성하는 제3 출력 회로부를 포함하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 4 | 제3 항에 있어서, 상기 제2 영역은 상기 반파장의 피크 중심 영역이고,상기 제1 영역은 상기 피크 중심 영역의 좌측의 임의의 영역이고,상기 제3 영역은 상기 피크 중심 영역의 우측의 임의의 영역인 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 5 | 제3 항에 있어서, 상기 제1, 제2 및 제3 출력 회로부는 각각, 트랜지스터;상기 트랜지스터를 통해 상기 변환 회로부터에서 출력되는 신호를 공급받아 타겟기준 신호를 생성하는 기준 신호 생성부; 및상기 반파장 입력 신호(VINN)와 타겟 기준 신호를 이용하여 타겟 게이트 신호를 생성하는 통합 비교기를 포함하되, 상기 타겟 게이트 신호는 상기 타겟 기준 신호가 목표 전압과 동일하도록 조절하되,상기 트랜지스터의 소스는 상기 변환 회로부와 연결되어 상기 반파장 입력 신호(VINN)를 공급받고, 상기 트랜지스터의 게이트는 상기 통합 비교기의 출력단과 연결되며, 상기 트랜지스터의 드레인은 상기 기준 신호 생성부의 출력단과 연결되되,상기 타겟 기준 신호는 제1 기준 신호(VREF,PL), 제2 기준 신호(VREF,PC) 및 제3 기준 신호(VREF,PR) 중 어느 하나이고,상기 타겟 게이트 신호는 제1 게이트 신호(VG,PL), 제2 게이트 신호(VG,PC) 및 제3 게이트 신호(VG,PC) 중 어느 하나인 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 6 | 제5 항에 있어서, 상기 제1 출력 회로부에 포함되는 통합 비교기는, 상기 반파장 입력 신호(VINN)와 상기 제1 기준 신호가 동일해지는 제1 시점을 감지하여 비교기 출력 신호(VCMP,PL)를 출력하는 비교기;상기 제1 기준 신호(VREF,PL)와 목표 전압(VTG,PL)을 비교하여 상기 비교기 출력 신호(VCMP,PL)의 지연을 결정하고, 상기 제1 게이트 신호(VG,PL)의 제2 시점(tP,PL)을 결정하여 상기 제1 기준 신호(VREF,PL)를 상기 목표 전압(VTG,PL)에 맞추도록 조절하는 PWM(pulse width modulation) 제어기; 및상기 제1 시점(tS,PL)에서 하강하고 상기 제2 시점(tS,PL)에서 상승하는 제1 게이트 신호를 출력하는 구동 회로부를 포함하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 7 | 제5 항에 있어서, 상기 제2 출력 회로부에 포함되는 통합 비교기는, 상기 반파장 입력 신호(VINN)와 상기 제2 기준 신호(VREF,PC)가 동일해지는 제3 시점(tS,PC)과 제4 시점(tE,PC)을 각각 감지하여 비교기 출력 신호(VCMP,PC)를 생성하는 비교기-상기 비교기 출력 신호(VCMP,PC)는 상기 제3 시점(tS,PC)에 하강하고 제4 시점(tE,PC)에 상승함;상기 제2 기준 신호(VREF,PC)와 목표 전압(VTG,PC)을 비교하여 상기 비교기 출력 신호(VCMP,PC)의 지연을 결정하고, 상기 제2 기준 신호(VREF,PC)를 상기 목표 전압(VTG,PC)에 맞추기 위한 제5 시점(tP,PC)을 결정하여 상기 제5 시점(tP,PC)에서 하강하는 출력 신호(VP,PC)를 생성하는 PWM 제어기; 및상기 비교기 출력 신호(VCMP,PC), 상기 PWM 제어기의 출력 신호(VP,PC)를 수신하여 상기 제3 시점(tS,PL)에서 하강하고 상기 제5 시점(tP,PC)에서 상승하는 제2 게이트 신호(VG,PC)를 생성하는 구동 회로부를 포함하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 8 | 제5 항에 있어서, 상기 제3 출력 회로부에 포함되는 통합 비교기는, 상기 반파장 입력 신호(VINN)와 상기 제3 기준 신호(VREF,PR)가 동일해지는 제6 시점(tE,PR)을 감지하여 비교기 출력 신호(VCMP,PR)를 생성하는 비교기;상기 제3 기준 신호(VREF,PR)와 목표 전압(VTG,PR)을 비교하여 상기 비교기 출력 신호(VCMP,PC)의 지연을 결정하고, 상기 제3 게이트 신호(VG,PR)가 하강하는 제7 시점(tP,PR)을 결정하여 상기 제3 기준 신호(VREF,PR)를 상기 목표 전압(VTG,PR)에 맞추도록 조절하는 출력 신호(VP,PR)를 생성하는 PWM 제어기; 및상기 제7 시점(tP,PR)에서 하강하고 상기 제6 시점(tE,PR)에서 상승하는 제3 게이트 신호(VG,PR)를 생성하는 구동 회로부를 포함하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 9 | 제8 항에 있어서, 상기 PWM 제어기는,상기 제3 기준 신호(VREF,PR)와 상기 목표 전압(VTG,PR)을 수신하여 출력 전류 신호(VOTA)를 생성하는 OTA 회로부;임계 전압과 상기 OTA 회로부의 출력 전류 신호(VOTA)를 입력받은 후 어느 하나를 출력하는 먹스(M5); 상기 먹스(M5)의 출력과 게이트가 연결되며, 상기 먹스(M5)를 통해 출력되는 출력 전류 신호(VOTA)에 의해 바이어스가 설정되어 바이어스 전류를 결정하는 바이어스 결정 회로부(N17); 및상기 바이어스 전류에 기초하여 상기 비교기 출력 신호(VCMP,PR)을 지연하여 상기 제3 기준 신호(VREF,PR)를 상기 목표 전압(VTG,PR)에 맞추도록 조절하는 출력 신호(VP,PR)를 생성하는 전류 조절 펄스 지연 회로부를 포함하되,상기 출력 전류 신호(VOTA)는 상기 제3 기준 신호(VREF,PR)가 상기 목표 전압(VTG,PR)을 초과하면 증가하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 10 | 제9 항에 있어서, 상기 먹스(M5)의 선택 신호(SPR,PRE)가 "0"인 경우, 상기 바이어스 결정 회로부(N17)는 차단 모드(cut-off mode)보다 높은 상기 임계 전압으로 바이어싱되는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 11 | 제8 항에 있어서, 상기 구동 회로부는, 상기 제7 시점(tP,PR)에서 하강하고 상기 제6 시점(tE,PR)에서 상승하는 제3 게이트 신호(VG,PR)를 생성함에 있어, 상기 제3 게이트 신호(VG,PR)가 상승할 때 상기 제2 기준 신호(VREF,PC)를 충전 경로를 통해 커패시터(C3)를 임계 전압(VTH)까지 충전하고, 상기 제3 게이트 신호(VG,PR)가 하강할 때 방전 경로를 통해 상기 커패시터(C3)를 방전하여 상기 제3 게이트 신호(VG,PR)를 네거티브 임계 전압(-VTH)으로 설정하는 네거티브 임계 게이트 구동 회로부를 포함하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 12 | 제3 항에 있어서,상기 제3 출력 회로부는, 상기 변환 회로부를 통해 입력되는 상기 반파장 입력 신호(VINN)가 감소하면서 기준 신호(VREF,PR)와 일치하는 지점을 기준 시작점으로 설정한 후 좌측 방향으로 게이트 폭 길이를 조절하여 제3 게이트 신호(VG,PR)를 생성하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 13 | 제8 항에 있어서,제3 출력 회로부에 포함되는 통합 비교기는, SR 래치 회로부를 가지며, 상기 비교기 출력 신호(VCMP,PR)는 R-입력 단자로 입력받고, 상기 종료점 보호 제어 신호는 S-입력 단자로 입력받은 후 상기 엔드 보호 신호에서 하강하고, 상기 제7 시점에서 상승하는 출력 신호(VQ,PR)를 생성하는 브리지 회로부를 더 포함하되, 상기 PWM 제어기는 상기 상기 브리지 회로부의 출력 신호(VQ,PR)를 지연하여 상기 제7 시점에서 하강하는 출력 신호(VP,PR)를 생성하는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |

| 14 | 제13 항에 있어서,상기 PWM 제어기는 포지티브 입력단자를 통해 기준 신호(VREF,PR)를 입력받고, 네거티브 입력단자를 통해 목표 전압(VTG,PR)을 교차로 입력받는 것을 특징으로 하는 단일-입력 다중-출력 공진 조정 정류기. |