| 번호 | 청구항 |

|---|---|

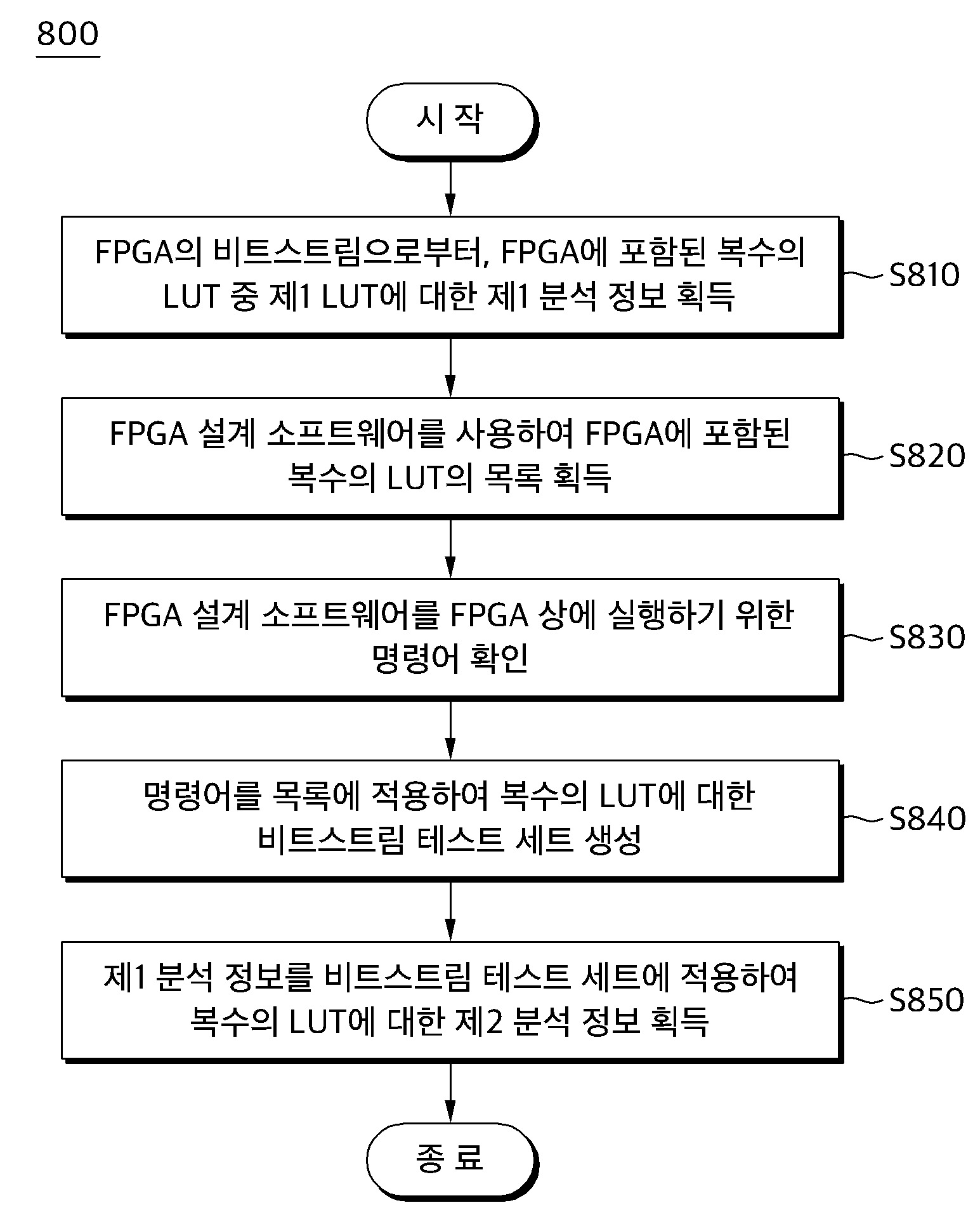

| 1 | 전자 장치가 FPGA(Field-Programmable Gate Array)를 분석하는 방법으로서,상기 FPGA의 비트스트림으로부터, 상기 FPGA에 포함된 복수의 LUT(Look Up Table) 중 제1 LUT에 대한 제1 분석 정보를 획득하는 단계;FPGA 설계 소프트웨어를 사용하여 상기 FPGA에 포함된 상기 복수의 LUT의 목록을 획득하는 단계;상기 FPGA 설계 소프트웨어를 상기 FPGA 상에 실행하기 위한 명령어를 확인하는 단계;상기 명령어를 상기 목록에 적용하여 상기 복수의 LUT에 대한 비트스트림 테스트 세트를 생성하는 단계; 및상기 제1 분석 정보를 상기 비트스트림 테스트 세트에 적용하여 상기 복수의 LUT에 대한 제2 분석 정보를 획득하는 단계를 포함하고,상기 제1 분석 정보를 획득하는 단계는상기 FPGA의 상기 비트스트림을 추출하는 단계;상기 비트스트림으로부터 상기 FPGA의 PLP(Programmable Logic Points) 정보를 추출하는 단계; 및상기 PLP 정보를 기반으로 상기 제1 LUT에 대한 역공학을 수행하는 단계를 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 2 | 제1항에 있어서,상기 제1 분석 정보는 상기 제1 LUT에 대한 비트스트림 변환 규칙 정보 및 상기 제1 LUT의 비트스트림 상 주소 정보를 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 3 | 삭제 |

| 4 | 제1항에 있어서,상기 비트스트림을 추출하는 단계는전원이 상기 FPGA에 인가된 후 메모리로부터 상기 FPGA로 다운로드되는 상기 비트스트림을 추출하는 단계를 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 5 | 제1항에 있어서,상기 복수의 LUT의 목록은 상기 FPGA에 포함된 CLB(Configurable Logic Block) 타일 구조에 대한 정보, 및 상기 CLB 타일 내 포함된 LUT에 대한 정보를 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 6 | 제1항에 있어서,상기 명령어는 FPGA 보드 설정 및 비트스트림 생성을 위한 제1 명령어와 회로 배치 및 배선 설정을 위한 제2 명령어 중 적어도 하나를 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 7 | 전자 장치가 FPGA를 분석하는 방법으로서,상기 FPGA의 비트스트림으로부터, 상기 FPGA에 포함된 복수의 LUT 중 제1 LUT에 대한 제1 분석 정보를 획득하는 단계;FPGA 설계 소프트웨어를 사용하여 상기 FPGA에 포함된 상기 복수의 LUT의 목록을 획득하는 단계;상기 FPGA 설계 소프트웨어를 상기 FPGA 상에 실행하기 위한 명령어를 확인하는 단계;상기 명령어를 상기 목록에 적용하여 상기 복수의 LUT에 대한 비트스트림 테스트 세트를 생성하는 단계; 및상기 제1 분석 정보를 상기 비트스트림 테스트 세트에 적용하여 상기 복수의 LUT에 대한 제2 분석 정보를 획득하는 단계를 포함하고,상기 비트스트림 테스트 세트는 상기 제1 분석 정보에 대응하는 논리 회로를 상기 복수의 LUT 중 상기 제1 LUT와 상이한 LUT에 배치하도록 생성되는, 전자 장치가 FPGA를 분석하는 방법. |

| 8 | 삭제 |

| 9 | 전자 장치가 FPGA를 분석하는 방법으로서,상기 FPGA의 비트스트림으로부터, 상기 FPGA에 포함된 복수의 LUT 중 제1 LUT에 대한 제1 분석 정보를 획득하는 단계;FPGA 설계 소프트웨어를 사용하여 상기 FPGA에 포함된 상기 복수의 LUT의 목록을 획득하는 단계;상기 FPGA 설계 소프트웨어를 상기 FPGA 상에 실행하기 위한 명령어를 확인하는 단계;상기 명령어를 상기 목록에 적용하여 상기 복수의 LUT에 대한 비트스트림 테스트 세트를 생성하는 단계; 및상기 제1 분석 정보를 상기 비트스트림 테스트 세트에 적용하여 상기 복수의 LUT에 대한 제2 분석 정보를 획득하는 단계를 포함하고,상기 제2 분석 정보는 상기 복수의 LUT의 상기 비트스트림 상 주소 정보를 포함하고,상기 방법은상기 복수의 LUT의 상기 비트스트림 상 주소 정보를 기반으로 상기 비트스트림을 분리하는 단계; 및상기 제1 분석 정보에 포함된 비트스트림 변환 규칙을 기반으로 상기 복수의 LUT 각각에 구현된 논리 회로를 획득하는 단계를 더 포함하는, 전자 장치가 FPGA를 분석하는 방법. |

| 10 | 비일시적 컴퓨터 판독 가능 저장 매체로서,컴퓨터 판독 가능 명령어들을 저장하도록 구성되는 매체를 포함하고,상기 컴퓨터 판독 가능 명령어들은 프로세서에 의해 실행되는 경우 상기 프로세서가:FPGA의 비트스트림으로부터, 상기 FPGA에 포함된 복수의 LUT 중 제1 LUT에 대한 제1 분석 정보를 획득하는 단계;FPGA 설계 소프트웨어를 사용하여 상기 FPGA에 포함된 상기 복수의 LUT의 목록을 획득하는 단계;상기 FPGA 설계 소프트웨어를 상기 FPGA 상에 실행하기 위한 명령어를 확인하는 단계;상기 명령어를 상기 목록에 적용하여 상기 복수의 LUT에 대한 비트스트림 테스트 세트를 생성하는 단계; 및상기 제1 분석 정보를 상기 비트스트림 테스트 세트에 적용하여 상기 복수의 LUT에 대한 제2 분석 정보를 획득하는 단계를 포함하는, 전자 장치가 FPGA를 분석하는 방법을 수행하도록 하고,상기 제1 분석 정보를 획득하는 단계는상기 FPGA의 상기 비트스트림을 추출하는 단계;상기 비트스트림으로부터 상기 FPGA의 PLP 정보를 추출하는 단계; 및상기 PLP 정보를 기반으로 상기 제1 LUT에 대한 역공학을 수행하는 단계를 포함하는, 비일시적 컴퓨터 판독 가능 저장 매체. |

| 11 | FPGA를 분석하는 전자 장치로서,적어도 하나의 명령어를 저장하는 메모리; 및상기 적어도 하나의 명령어를 실행함으로써, 상기 FPGA의 비트스트림으로부터, 상기 FPGA에 포함된 복수의 LUT 중 제1 LUT에 대한 제1 분석 정보를 획득하고, FPGA 설계 소프트웨어를 사용하여 상기 FPGA에 포함된 상기 복수의 LUT의 목록을 획득하고, 상기 FPGA 설계 소프트웨어를 상기 FPGA 상에 실행하기 위한 명령어를 확인하고, 상기 명령어를 상기 목록에 적용하여 상기 복수의 LUT에 대한 비트스트림 테스트 세트를 생성하고, 상기 제1 분석 정보를 상기 비트스트림 테스트 세트에 적용하여 상기 복수의 LUT에 대한 제2 분석 정보를 획득하는 프로세서를 포함하고,상기 제1 분석 정보를 획득하는 것은:상기 FPGA의 상기 비트스트림을 추출하고,상기 비트스트림으로부터 상기 FPGA의 PLP 정보를 추출하고,상기 PLP 정보를 기반으로 상기 제1 LUT에 대한 역공학을 수행하는 것을 포함하는, FPGA를 분석하는 전자 장치. |