| 번호 | 청구항 |

|---|---|

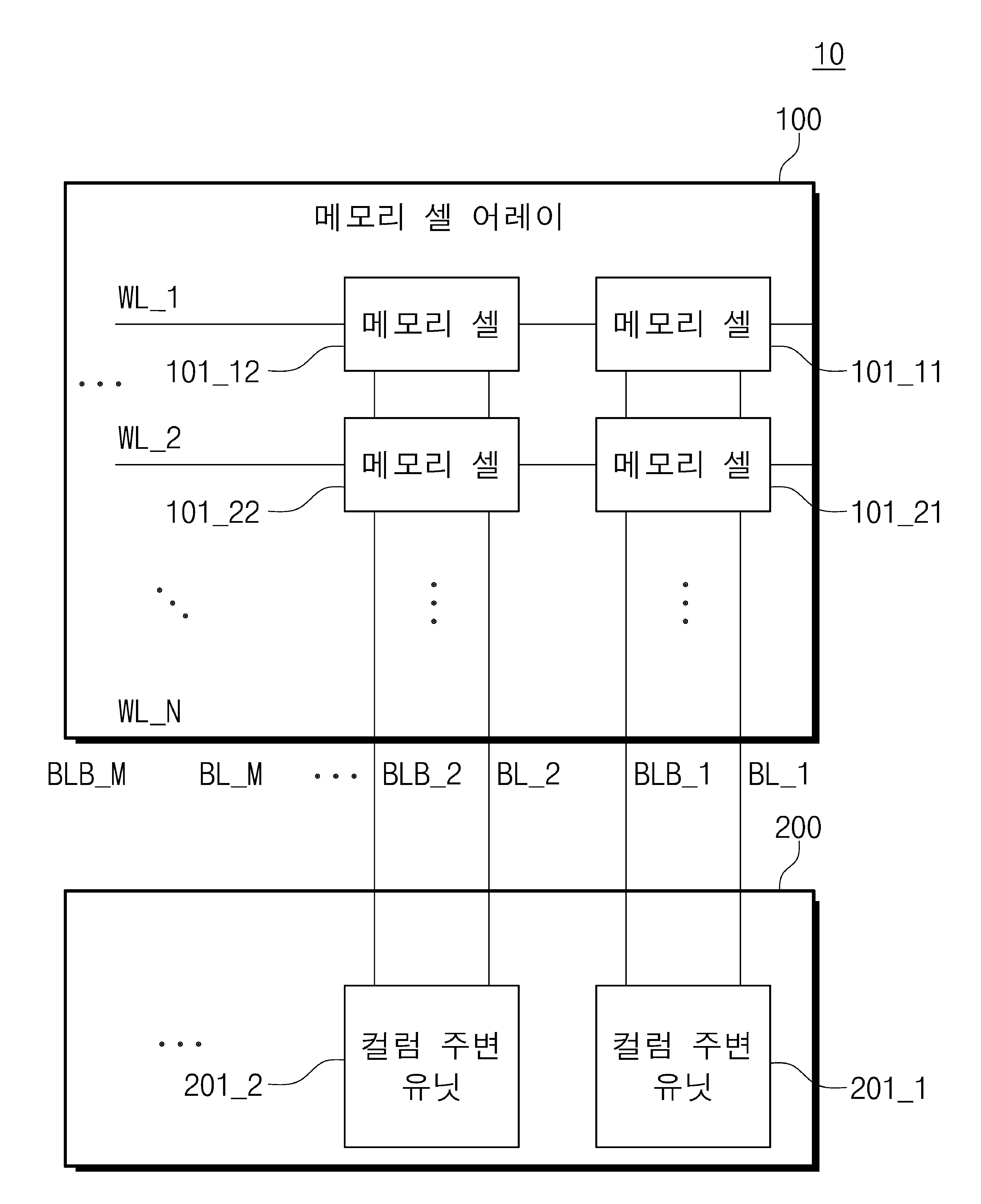

| 1 | 메모리 셀 어레이; 및상기 메모리 셀 어레이에 연결된 복수의 비트라인쌍들에 연결되는 복수의 컬럼 주변 유닛들을 포함하는 컬럼 주변 회로를 포함하고,상기 컬럼 주변 유닛들 각각은 상기 복수의 비트라인쌍들 중 하나의 비트라인 쌍을 통해 비트와이즈 데이터를 감지 증폭하는 감지증폭 및 라이트부; 및상기 비트와이즈 데이터에 기초하여, 전가산기 불 함수 기반의 산술 연산을 수행하고, 상기 산술 연산에 따라 획득되는 연산 데이터에 대해 상기 감지증폭 및 라이트부를 통해 라이트 백 동작을 수행시키는 연산 로직부를 포함하는, 인메모리 컴퓨팅. |

| 2 | 제1항에 있어서, 상기 연산 데이터는 NAND, AND, NOR, OR, XNOR, XOR, NOT, Shift 연산 값을 포함하는 로직 데이터와 ADD, ADD-Shift, SUB, MULT 연산 값을 정수 데이터 중 어느 하나를 포함하는, 인메모리 컴퓨팅. |

| 3 | 제2항에 있어서, 상기 연산 로직부는 하위 비트 측으로부터 제1 캐리값을 출력받는 제1 멀티플렉서;상기 하위 비트 측으로부터 제1 합산값을 출력받는 시프트 플립플롭; 상기 제1 캐리값, 상기 제1 합산값 및 상기 감지증폭 및 라이트부를 감지된 비트와이즈 데이터에 기초하여, 제2 캐리값과 제2 합산값을 연산하는 전가산기 로직; 상기 제2 합산값을 출력받아 상위 비트측으로 전달하는 제2 멀티플렉서; 및상기 제1 캐리값, 상기 제1 합산값, 상기 제2 합산값 및 상기 비트와이즈 데이터 중 적어도 하나를 출력받는 제3 멀티플렉서를 포함하는, 인메모리 컴퓨팅. |

| 4 | 제3항에 있어서,상기 제3 멀티플렉서는 상기 제1 캐리값, 상기 제1 합산값, 상기 제2 합산값 및 상기 비트와이즈 데이터 중 적어도 하나를 상기 감지증폭 및 라이트부를 통해 라이트 백 시키는, 인메모리 컴퓨팅. |

| 5 | 제3항에 있어서, 상기 전가산기 로직은 상기 제1 멀티플렉서로부터 전송받는 선택 신호에 따라 스위칭되는 전송 게이트 기반의 회로로 구현된, 인메모리 컴퓨팅. |

| 6 | 제3항에 있어서, 상기 컬럼 주변 회로는 상기 비트와이즈 데이터를 상위 비트 측 방향으로 전달하는 Shift 연산을 수행하는, 인메모리 컴퓨팅. |

| 7 | 제6항에 있어서,상기 컬럼 주변 회로는 상기 Shift 연산이 수행되는 단일 주기에서, 상기 복수의 연산 로직부들을 통해 수행되는 모든 Shift 연산 동작을 한번에 수행하는, 인메모리 컴퓨팅. |

| 8 | 제3항에 있어서, 상기 컬럼 주변 회로는 상기 제2 캐리값을 상위 비트 측 방향으로 전달하고, 상기 제2 합산값을 라이트 백 시키는 ADD 연산을 수행하는, 인메모리 컴퓨팅. |

| 9 | 제8항에 있어서, 상기 컬럼 주변 회로는 상기 ADD 연산이 수행되는 단일 주기에서, 상기 복수의 연산 로직부들을 통해 수행되는 모든 ADD 연산 동작을 한번에 수행하는, 인메모리 컴퓨팅. |

| 10 | 제3항에 있어서, 상기 컬럼 주변 회로는 상기 제2 합산값을 상위 비트 측 방향으로 전달함에 따라, 하위 비트 측으로부터 전달받는 상기 제1 합산값을 라이트 백 시키는 ADD-Shift 연산 동작을 수행하는, 인메모리 컴퓨팅. |

| 11 | 제10항에 있어서, 상기 ADD-Shift 연산이 수행되는 주기는 상기 제2 합산값을 상위 비트 측 방향으로 전달하는 제1 주기와 상기 제1 합산값을 라이트 백 시키는 제2 주기를 포함하는, 인메모리 컴퓨팅. |

| 12 | 메모리 셀 어레이;상기 메모리 셀 어레이에 연결된 복수의 컬럼 주변 유닛들을 포함하는 컬럼 주변 회로부;상기 메모리 셀 어레이에 저장된 피승수 데이터를 저장하는 더미셀 어레이부;상기 더미셀 어레이와 상기 메모리 셀 어레이를 분리시키는 BL 세퍼레이터부; 및상기 메모리 셀 어레이로부터 로드되는 승수 데이터에 기초하여, 상기 복수의 컬럼 주변 유닛들의 곱셈 연산 동작을 제어하는 시프트 레지스터 회로를 포함하는, 인메모리 컴퓨팅. |

| 13 | 제12항에 있어서, 상기 더미셀 어레이부는 0의 데이터를 저장하는 제1 서브 어레이;상기 피승수 데이터를 최하위 비트에서 최상위 비트 순서로 저장하는 제2 서브 어레이; 및상기 복수의 컬럼 주변 유닛들을 통해 라이트 백 되는 임시 데이터를 저장하는 제3 서브 어레이를 포함하는, 인메모리 컴퓨팅. |

| 14 | 제12항에 있어서, 상기 시프트 레지스터 회로는 상기 승수 데이터가 최상위 비트에서 최하위 비트 순서로 출력되는 로드 데이터를 저장하는 복수의 승수 플립플롭들; 및상기 로드 데이터에 기초하여, 상기 복수의 컬럼 주변 유닛들을 제어하기 위한 제어 신호를 전송하는 복수의 제어 멀티플렉서들을 포함하는, 인메모리 컴퓨팅. |

| 15 | 제13항에 있어서, 상기 복수의 컬럼 주변 유닛들은 상기 승수 데이터의 최상위 비트에 대응되는 제어 신호에 기초하여, 상기 제1 및 제2 서브 어레이 대한 컬럼별 ADD-Shift 연산 동작을 수행하는, 인메모리 컴퓨팅. |

| 16 | 제13항에 있어서,상기 복수의 컬럼 주변 유닛들은 상기 승수 데이터의 중간 비트가 0에 대응되는 제어 신호에 기초하여, 상기 제3 서브 어레이에 대한 Shift 연산 동작을 수행하는, 인메모리 컴퓨팅. |

| 17 | 제13항에 있어서,상기 복수의 컬럼 주변 유닛들은 상기 승수 데이터의 중간 비트가 1에 대응되는 제어 신호에 기초하여, 상기 제2 및 제3 서브 어레이에 대한 컬럼별 ADD-Shift 연산 동작을 수행하는, 인메모리 컴퓨팅. |

| 18 | 제13항에 있어서, 상기 복수의 컬럼 주변 유닛들은 상기 승수 데이터의 최하위 비트에 대응되는 제어 신호에 기초하여, 상기 제2 및 제3 서브 어레이에 대한 ADD 연산 동작을 수행하는, 인메모리 컴퓨팅. |

| 19 | 제13항에 있어서, 상기 복수의 컬럼 주변 유닛들 각각은 하위 비트 측으로부터 제1 캐리값을 출력받는 제1 멀티플렉서;상기 하위 비트 측으로부터 제1 합산값을 출력받는 시프트 플립플롭; 상기 제1 캐리값, 상기 제1 합산값 및 감지증폭 및 라이트부를 통해 감지된 비트와이즈 데이터에 기초하여, 제2 캐리값과 제2 합산값을 연산하는 전가산기 로직; 상기 제2 합산값을 출력받아 상위 비트측으로 전달하는 제2 멀티플렉서; 및상기 제1 캐리값, 상기 제1 합산값, 상기 제2 합산값 및 상기 비트와이즈 데이터 중 적어도 하나를 출력받는 제3 멀티플렉서를 포함하는, 인메모리 컴퓨팅. |

| 20 | 제19항에 있어서, 상기 전가산기 로직은 상기 제1 멀티플렉서로부터 전송받는 선택 신호에 따라 스위칭되는 전송 게이트 기반의 회로로 구현된, 인메모리 컴퓨팅. |