| 번호 | 청구항 |

|---|---|

| 3 | 제1항에 있어서, 상기 적어도 한 쌍의 워드 라인에 인가되는 워드 라인 신호의 펄스 폭은 프리차징 전압이 디스차징되는 시간 구간보다 짧은 폭을 갖고, 상기 프리차징 전압의 전압 레벨에 대응되는 진폭을 갖는 펄스 신호인, 컴퓨팅 인 메모리. |

| 4 | 제1항에 있어서, 상기 주변 회로는 상기 적어도 하나의 비트 라인이 가속화 대상으로 판단된 경우, 상기 적어도 하나의 비트 라인에 대하여 상기 디스차징 동작을 수행하고, 상기 적어도 하나의 비트 라인이 유지 대상으로 판단된 경우, 상기 디스차징 동작을 차단시키는, 컴퓨팅 인 메모리. |

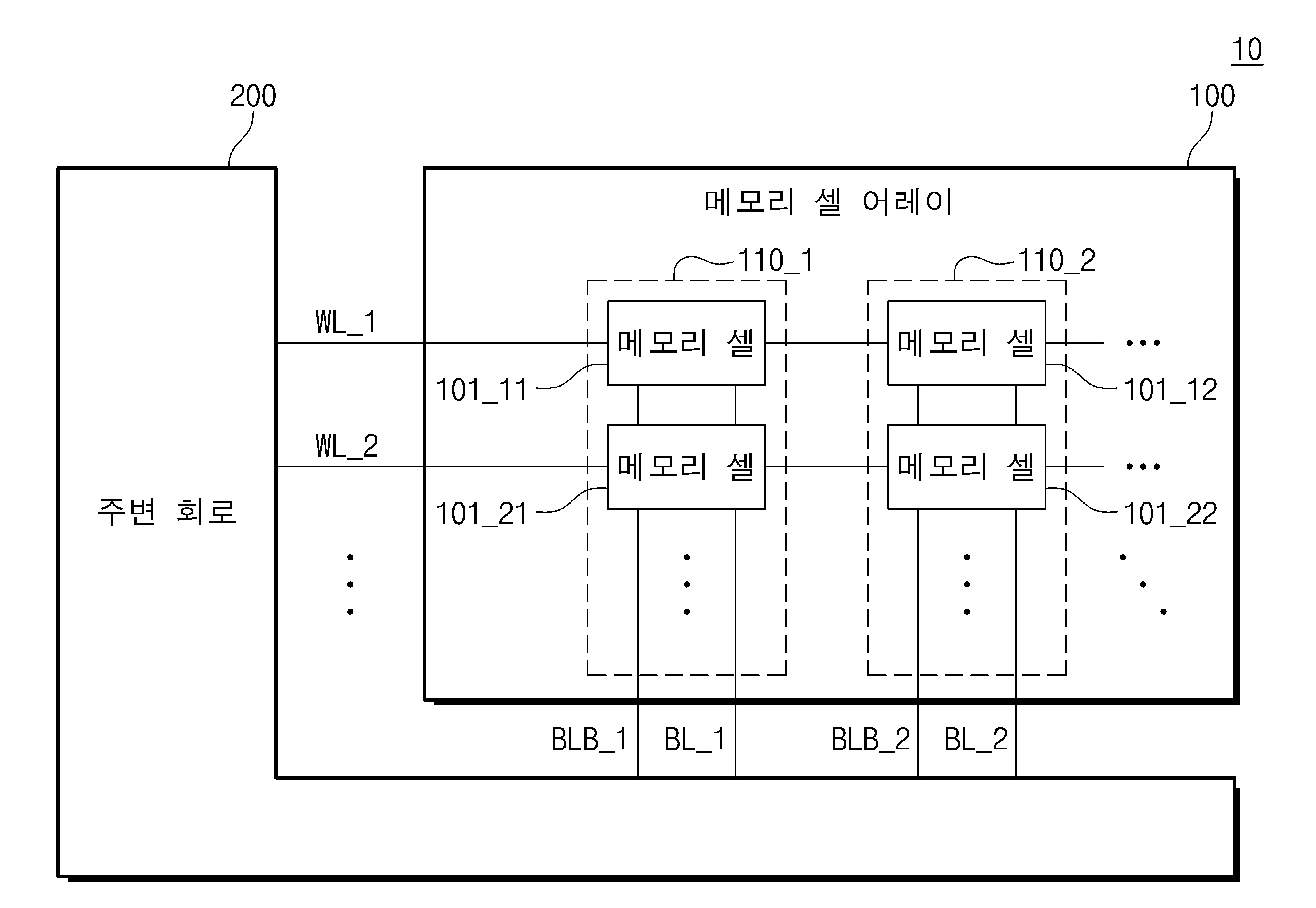

| 1 | 적어도 한 쌍의 워드 라인, 적어도 한 쌍의 비트 라인 및 상기 적어도 한 쌍의 워드 라인 및 상기 적어도 한 쌍의 비트 라인에 연결되는 적어도 한 쌍의 메모리 셀을 포함하는 메모리 셀 어레이; 및상기 적어도 한 쌍의 비트 라인을 통해 상기 적어도 한 쌍의 메모리 셀에 연결되고, 상기 적어도 한 쌍의 비트 라인의 전압 레벨에 기초하여, 상기 적어도 한 쌍의 비트 라인 중 적어도 하나의 비트 라인에 대한 디스차징 동작을 수행하는 주변 회로를 포함하고,상기 주변 회로는 상기 적어도 한 쌍의 비트 라인의 각 전압 레벨에 기초하여, 상기 적어도 한 쌍의 비트 라인 각각에 대한 가속화 대상 여부를 판단하는, 컴퓨팅 인 메모리. |

| 2 | 삭제 |

| 5 | 제1항에 있어서, 상기 주변 회로는 상기 적어도 한 쌍의 워드 라인을 통해 상기 메모리 셀 어레이에 연결된 워드라인 구동부; 상기 적어도 한 쌍의 비트 라인을 통해 상기 적어도 한 쌍의 메모리 셀에 연결된 가속화 회로부; 및기 설정된 제1 내지 제3 동작 구간 동안 순차적으로 상기 워드 라인 구동부와 상기 가속화 회로부를 제어하는 제어부를 포함하는, 컴퓨팅 인 메모리. |

| 6 | 제5항에 있어서, 상기 제어부는 상기 제1 동작 구간 동안, 상기 적어도 하나의 비트 라인을 프리차징 시키기 위한 프리차징 신호와 상기 가속화 회로부에 포함된 하나의 미러 노드를 리셋하기 위한 리셋 신호를 상기 가속화 회로부에 출력하는, 컴퓨팅 인 메모리. |

| 7 | 제6항에 있어서, 상기 제어부는 상기 제2 동작 구간 동안, 상기 디스차징 동작을 수행하기 위한 인에이블 신호를 상기 가속화 회로부에 출력하는, 컴퓨팅 인 메모리. |

| 8 | 제7항에 있어서,상기 제어부는 상기 제2 동작 구간 동안, 상기 워드 라인 구동부를 제어하기 위한 워드 라인 제어 신호를 상기 워드 라인 구동부에 출력하는, 컴퓨팅 인 메모리. |

| 9 | 제8항에 있어서, 상기 제어부는 상기 제3 동작 구간 동안, 상기 인에이블 신호를 상기 가속화 회로부에 출력하는, 컴퓨팅 인 메모리. |

| 10 | 제7항에 있어서, 상기 가속화 회로부는 상기 적어도 하나의 비트 라인을 프리차징 하기 위한 제1 내지 제3 프리차징 트랜지스터; 및상기 디스차징 동작을 수행하기 위한 제1 및 제2 부스터를 포함하는, 컴퓨팅 인 메모리. |

| 11 | 제10항에 있어서, 상기 제1 및 제2 부스터 각각은, 일측이 상기 적어도 하나의 비트 라인에 연결된 제1 부스트 트랜지스터;게이트측이 상기 제1 부스트 트랜지스터의 일측에 연결되고, 일측이 전압원에 연결된 제2 부스트 트랜지스터;게이트측이 상기 제1 부스트 트랜지스터의 일측에 연결되고, 일측이 상기 제2 부스트 트랜지스터의 타측에 연결된 제3 부스트 트랜지스터;상기 리셋 신호에 기초하여, 상기 제3 부스트 트랜지스터의 타측과 접지를 스위칭 연결하는 제4 부스트 트랜지스터; 및상기 인에이블 신호에 기초하여, 상기 제1 부스트 트랜지스터의 타측과 접지를 스위칭 연결하는 제5 부스트 트랜지스터를 포함하는, 컴퓨팅 인 메모리. |

| 12 | 제11항에 있어서,상기 제1 및 제3 내지 제5 부스트 트랜지스터는 NMOS 트랜지스터이고, 상기 제2 부스트 트랜지스터는 PMOS 트랜지스터인, 컴퓨팅 인 메모리. |

| 13 | 제11항에 있어서,상기 적어도 하나의 비트 라인과 상기 제1 부스트 트랜지스터의 일측이 교차되는 비트라인 노드의 전압 레벨이 프리차징 전압보다 작은 경우, 상기 제1 내지 제3 부스트 트랜지스터는 스위칭 온 되는, 컴퓨팅 인 메모리. |

| 14 | 제13항에 있어서,상기 비트라인 노드의 전압 레벨이 상기 프리차징 전압에 대응되는 경우, 상기 제1 및 제2 부스트 트랜지스터는 스위칭 오프되고, 상기 제3 부스트 트랜지스터는 스위칭 온 되는, 컴퓨팅 인 메모리. |

| 15 | 제5항에 있어서, 상기 주변 회로는 상기 메모리 셀 어레이와 상기 가속화 회로부 사이에 위치하는 BL 세퍼레이터부; 및상기 BL 세퍼레이터부와 상기 가속화 회로부 사이에 위치하는 더미 어레이부를 더 포함하는, 컴퓨팅 인 메모리. |

| 16 | 컴퓨팅 인 메모리에 의해 수행되는 컴퓨팅 인 메모리 기반 제어 동작 방법으로서, 제어부가 프리차징 신호와 리셋 신호를 가속화 회로부에 출력하는 단계; 및상기 제어부가 인에이블 신호를 상기 가속화 회로부에 출력하는 동시에, 워드 라인 제어 신호를 워드 라인 구동부에 출력하는 단계를 포함하는, 컴퓨팅 인 메모리 기반 제어 동작 방법. |

| 17 | 제16항에 있어서, 상기 워드 라인 구동부에 출력하는 단계는: 상기 워드 라인 구동부가 상기 워드 라인 제어 신호에 기초하여, 워드 라인 신호를 적어도 한 쌍의 비트 라인에 연결된 적어도 한 쌍의 메모리 셀에 출력하는 단계를 포함하는, 컴퓨팅 인 메모리 기반 제어 동작 방법. |

| 18 | 제17항에 있어서, 상기 워드 라인 신호는 프리차징 전압이 디스차징되는 구간보다 짧은 폭을 갖고, 상기 프리차징 전압의 레벨에 대응되는 크기를 갖는 펄스 신호인, 컴퓨팅 인 메모리 기반 제어 동작 방법. |