| 번호 | 청구항 |

|---|---|

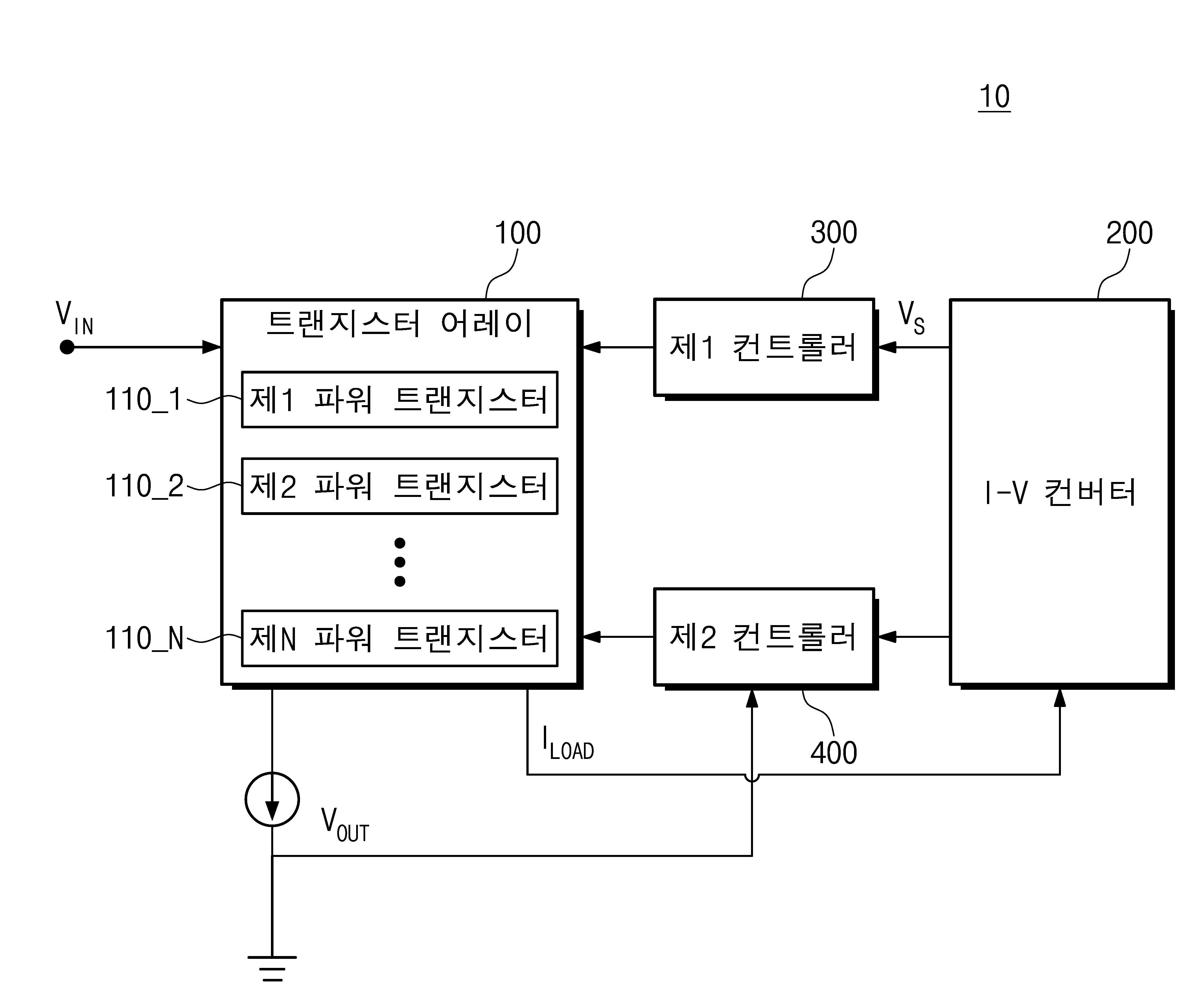

| 1 | 복수의 파워 트랜지스터들을 포함하는 트랜지스터 어레이;상기 트랜지스터 어레이로부터 로드된 로드전류를 동작전압으로 변환하는 I-V 컨버터; 상기 동작전압에 기초하여, 상기 복수의 파워 트랜지스터들 중 적어도 하나의 파워 트랜지스터를 턴-온시키는 제1 컨트롤러; 및상기 트랜지스터 어레이로부터 출력되는 출력전압에 기초하여, 상기 복수의 파워 트랜지스터들 중 턴-온되는 적어도 하나의 파워 트랜지스터의 게이트 오버드라이브 전압(Gate overdrive voltage)을 조절하는 제2 컨트롤러를 포함하고,상기 제1 컨트롤러는, 상기 동작전압과 램프신호를 비교하여 기준신호를 생성하는 제1 비교부; 및상기 기준신호를 일정시간마다 딜레이시켜 복수의 딜레신호들을 생성하는 복수의 딜레이셀들을 포함하는 제1 제어부를 포함하는 이중모드 LDO 레귤레이터. |

| 2 | 삭제 |

| 3 | 제1항에 있어서, 상기 제1 제어부는, 상기 기준신호의 하이구간에서, 하이상태인 딜레이신호의 개수에 따라, 상기 복수의 파워 트랜지스터들 중 턴-온되는 적어도 하나의 파워 트랜지스터의 개수를 조절하는 이중모드 LDO 레귤레이터. |

| 4 | 제3항에 있어서, 상기 제1 제어부는, 상기 복수의 딜레신호들의 하이 상태인 상승구간에서, 상승이 시작되는 데드타임(Dead-Time)을 검출하는 상승에지 검출기를 더 포함하고, 상기 기준신호의 하이 구간과 상기 데드타임을 제외한 동작구간을 비교하는 이중모드 LDO 레귤레이터. |

| 5 | 제1항에 있어서, 상기 제2 컨트롤러는, 상기 동작전압과 기준전압에 따라, 업-다운신호와 에러보상클럭을 출력하는 에러-제어 보상부; 및 상기 업-다운신호와 상기 에러보상클럭에 따라, 상기 적어도 하나의 파워 트랜지스터의 게이트전압을 조절하는 멀티-스텝 전하펌프부를 포함하는 이중모드 LDO 레귤레이터. |

| 6 | 제5항에 있어서, 상기 제2 컨트롤러는, 상기 업-다운신호가 연속적으로 일정 개수 이상 동일하게 출력될 때, 상기 제1 컨트롤러를 리셋시키는 이중모드 LDO 레귤레이터. |

| 7 | 제5항에 있어서, 상기 에러-제어 보상부는, 상기 출력전압과 기준전압을 비교하여 상기 업-다운신호를 생성하는 제2 비교부; 상기 업-다운신호에 기초하여, AND 게이트와 다수의 적분기들을 통해 보상되는 에러보상클럭을 상기 멀티-스텝 전하펌프부에 제공하는 클럭제공부; 및상기 에러보상클럭을 상기 제2 비교부에 피드백시키는 피드백부를 포함하는 이중모드 LDO 레귤레이터. |

| 8 | 제5항에 있어서, 상기 멀티-스텝 전하펌프부는, 입력전압이 제공되는 입력노드와 상기 적어도 하나의 파워 트랜지스터의 게이트를 전기적으로 연결하는 이중모드 LDO 레귤레이터. |

| 9 | 제8항에 있어서, 상기 멀티-스텝 전하펌프부는, 복수의 충전 커패시터들을 포함하는 커패시터 어레이;상기 커패시터 어레이의 일 측과 접지를 연결하는 제1 스위칭부; 상기 커패시터 어레이의 일 측과 상기 적어도 하나의 파워 트랜지스터의 게이트를 연결하는 제2 스위칭부; 상기 입력노드와 상기 적어도 하나의 파워 트랜지스터의 게이트 사이에 병렬로 위치한 게이트측 커패시터; 및상기 커패시터 어레이의 타 측을 상기 입력노드 및 접지 중 어느 하나에 연결하는 제3 스위칭부를 포함하는 이중모드 LDO 레귤레이터. |

| 10 | 제9항에 있어서, 상기 멀티-스텝 전하펌프부는, 상기 업-다운신호를 일정 클럭주기마다 교대로 출력하는 D 플립플롭; 및상기 에러보상클럭에 따라, 제1 및 제2 스위칭신호를 출력하는 커패시터 컨트롤러를 포함하는 이중모드 LDO 레귤레이터. |

| 11 | 제10항에 있어서, 상기 커패시터 컨트롤러는, 상기 일정 클럭주기에서 상기 제1 및 제2 스위칭신호와 상기 업-다운신호에 기초하여, 제3 스위칭신호를 생성하는 낸드회로부를 포함하는 이중모드 LDO 레귤레이터. |

| 12 | 제11항에 있어서, 상기 낸드회로부는, 상기 업-다운신호의 업신호와 상기 제2 스위칭신호를 입력으로 하는 제1 낸드게이트;상기 다운신호와 상기 제1 스위칭신호를 입력으로 하는 제2 낸드게이트; 및상기 제1 및 제2 낸드게이트로부터 출력된 출력값들을 입력받아 상기 제3 스위칭부를 스위칭시키는 스위칭신호를 출력하는 제3 낸드게이트를 포함하는 이중모드 LDO 레귤레이터. |

| 13 | 제10항에 있어서, 상기 커패시터 컨트롤러는, 상기 동작전압에 따라, 상기 복수의 커패시터들 중 활성화되는 적어도 하나의 커패시터의 개수를 조절하는 이중모드 LDO 레귤레이터. |

| 14 | 제13항에 있어서, 상기 커패시터 컨트롤러는, 상기 복수의 커패시터들 중 활성화된 적어도 하나의 커패시터의 개수에 기초하여, 상기 게이트전압의 변화속도를 조절하는 이중모드 LDO 레귤레이터. |

| 15 | 제14항에 있어서, 상기 게이트전압은, 상기 게이트 커패시터 대 상기 복수의 커패시터들 중 활성화된 적어도 하나의 커패시터 간의 용량비와 상기 입력전압을 곱한 값인 이중모드 LDO 레귤레이터. |

| 16 | 제15항에 있어서, 상기 커패시터 어레이가 게이트 측 노드와 입력노드를 전기적으로 연결할 때, 상기 커패시터 컨트롤러는, 상기 커패시터 어레이에 충전된 전위차에 따라, 상기 게이트전압을 양(+)의 전압으로 증가시키는 이중모드 LDO 레귤레이터. |

| 17 | 제13항에 있어서, 상기 커패시터 어레이가 게이트 측 노드와 접지를 전기적으로 연결할 때, 상기 커패시터 컨트롤러는, 상기 커패시터 어레이에 충전된 전위차에 따라, 상기 게이트전압을 음(-)의 전압으로 감소시키는 이중모드 LDO 레귤레이터. |

| 18 | 이중모드 LDO 레귤레이터의 동작방법에 있어서, 복수의 파워 트랜지스터들을 포함하는 트랜지스터 어레이를 통해 입력전압을 입력받는 단계;상기 입력전압에 따라 상기 트랜지스터 어레이를 통해 로드된 로드전류를 피드백 받고, 동작전압으로 변환하는 단계;상기 동작전압에 기초하여, 상기 복수의 파워 트랜지스터들 중 적어도 하나의 파워 트랜지스터를 턴-온시키는 단계; 및상기 트랜지스터 어레이로부터 출력되는 출력전압에 기초하여, 상기 복수의 파워 트랜지스터들 중 턴-온된 적어도 하나의 파워 트랜지스터의 게이트 오버드라이브 전압을 조절하는 단계를 포함하고, 상기 턴-온시키는 단계는, 상기 동작전압과 비교되기 위한 램프신호를 생성하는 단계;상기 램프신호와 상기 동작전압을 비교하여 기준신호를 생성하는 단계;상기 기준신호를 일정시간마다 딜레이 시켜, 복수의 딜레이신호들을 생성하는 단계; 및상기 기준신호와 상기 복수의 딜레이신호들에 기초하여, 상기 적어도 하나의 파워 트랜지스터의 개수를 조절하는 단계를 포함하는 이중모드 LDO 레귤레이터의 동작방법. |

| 19 | 삭제 |

| 20 | 제18항에 있어서, 상기 적어도 하나의 파워 트랜지스터의 개수를 조절하는 단계는, 상기 기준신호의 하이 구간에서, 상기 복수의 딜레이신호들 중 하이 상태인 딜레이신호를 탐지하는 단계; 및상기 하이 상태인 딜레이신호의 개수에 따라, 상기 적어도 하나의 파워 트랜지스터의 개수를 결정하는 단계를 포함하는 이중모드 이중모드 LDO 레귤레이터의 동작방법. |

| 21 | 제18항에 있어서, 상기 게이트 오버드라이브 전압을 조절하는 단계는, 상기 출력전압과 기준전압을 비교하여, 업-다운신호와 에러보상클럭을 생성하는 단계;상기 출력전압과 기준전압간의 차이에 따라, 커패시터 어레이의 복수의 충전 커패시터들 중 적어도 하나의 충전 커패시터를 활성화시키는 단계;상기 업-다운신호와 에러보상클럭에 따라 출력되는 제1 내지 제3 스위칭신호에 기초하여, 상기 적어도 하나의 충전 커패시터를 충전시키는 단계; 및상기 적어도 하나의 충전 커패시터에 충전된 전위차에 기초하여, 상기 적어도 하나의 파워 트랜지스터의 게이트전압을 조절하는 단계를 포함하는 이중모드 LDO 레귤레이터의 동작방법. |