| 번호 | 청구항 |

|---|---|

| 1 | 반도체 채널층, 제어 게이트 전극층, 상기 반도체 채널층과 상기 제어 게이트 전극층 사이의 내부 전극층, 적어도 상기 제어 게이트 전극층과 상기 내부 전극층 사이에 개재된 강유전체층 및 상기 내부 전극층에 연결된 전류 제어 소자을 포함하는 강유전체 메모리 소자의 멀티레벨 동작방법으로서,상기 제어 게이트 전극층에 프로그램 전압을 인가하는 프로그램 단계;상기 내부 전극을 통한 변위 전류를 제어하여 상기 강유전체층의 분극 레벨을 멀티레벨로 제어하는 변위 전류 제어 단계: 및상기 제어 게이트 전극층에 읽기 전압을 인가하는 검증 단계를 포함하고,상기 변위 전류 제어 단계에서, 상기 전류 제어 소자를 통해서 상기 내부 전극층을 통한 변위 전류를 제어하여 상기 강유전체층의 분극 레벨을 멀티레벨로 제어하는,강유전체 메모리 소자의 멀티레벨 동작방법. |

| 2 | 제 1 항에 있어서,상기 변위 전류 제어 단계에서, 상기 변위 전류를 크게 할수록 상기 강유전체 메모리 소자의 문턱전압이 낮아지는, 강유전체 메모리 소자의 멀티레벨 동작방법. |

| 3 | 제 1 항에 있어서,상기 전류 제어 소자는 바이폴라 정션 트랜지스터를 포함하고,상기 변위 전류 제어 단계에서, 상기 바이폴라 정션 트랜지스터의 베이스 단자로 유입되는 전류를 변화시켜 상기 내부 전극층을 통한 변위 전류를 제어하는,강유전체 메모리 소자의 멀티레벨 동작방법. |

| 4 | 제 3 항에 있어서,상기 베이스 단자는 저항을 통해서 베이스 전원부에 연결되고,상기 변위 전류 제어 단계에서, 상기 베이스 단자로 유입되는 전류의 변화는 상기 베이스 전원부의 인가 전압을 변화시켜 수행하는,강유전체 메모리 소자의 멀티레벨 동작방법. |

| 5 | 제 1 항에 있어서,상기 프로그램 단계, 상기 변위 전류 제어 단계 및 상기 검증 단계는, 상기 강유전체층의 분극 레벨을 변화시키도록 상기 변위 전류를 변화시켜 가면서 복수회 반복되는,강유전체 메모리 소자의 멀티레벨 동작방법. |

| 6 | 제 5 항에 있어서,상기 검증 단계 후 상기 프로그램 단계를 반복하기 전에 상기 제어 게이트 전극층에 소거 전압을 인가하는 소거 단계를 수행하는, 강유전체 메모리 소자의 멀티레벨 동작방법. |

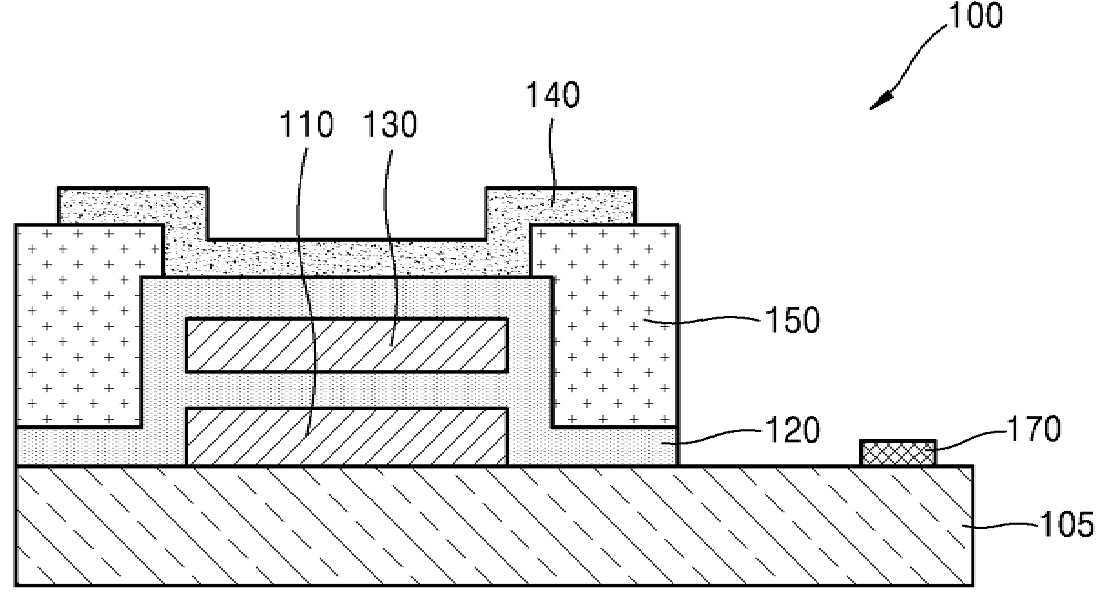

| 7 | 제 1 항에 있어서,상기 강유전체 메모리 소자에서, 상기 제어 게이트 전극층 및 상기 반도체 채널층은 기판 상에 형성되고,상기 전류 제어 소자는 상기 기판에 형성되는,강유전체 메모리 소자의 멀티레벨 동작방법. |

| 8 | 제 7 항에 있어서,상기 반도체 채널층은 상기 기판 상에 수직하게 연장된 원통 형태로 배치되고,상기 강유전체층은 상기 반도체 채널층의 외주면 상에 배치되고,상기 제어 게이트 전극층은 상기 강유전체층 외측에 배치되고,상기 내부 전극층은 상기 제어 게이트 전극층 및 상기 반도체 채널층 사이에 배치된,강유전체 메모리 소자의 멀티레벨 동작방법. |